# Tracing Correctness: A Practical Approach to Traceable Runtime Monitoring

Saarland University

Department of Computer Science

Master's Thesis

submitted by

Jan Eric Baumeister

Saarbrücken, February 2020

Supervisor: Prof. Bernd Finkbeiner, Ph.D.

Advisor: Maximilian Schwenger

Sebastian Schirmer

Reviewer: Prof. Bernd Finkbeiner, Ph.D.

Prof. Dr.-Ing. Stefan Levedag

Submission: 10 February, 2020

#### **Abstract**

The established approach to check the correctness of a cyber-physical system is to verify all possible executions statically. With their increasing autonomy, verifying all traces develops into a harder problem. To handle the increased complexity, runtime monitoring verifies the system dynamically.

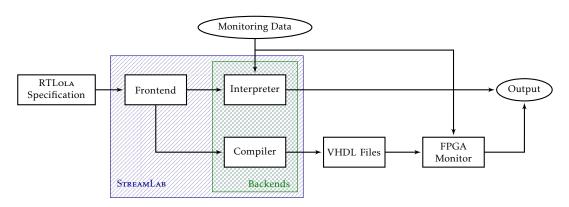

RTLola is a stream-based specification language to express complex real-time constraints that provides different static analyses as the determination of an upper bound on the required memory. The underlying monitoring framework, Streamlar, uses these analyses and interprets the given RTLola specification. However, to find an industrial application for aerial vehicles, a certification by the Federal Aviation Administration (FAA) or the European Union Aviation Safety Agency (EASA) is needed. Part of this certification process is to show that the product is traceable, i.e., describing the relationship between the specification language and the software. One advantage of a traceable implementation is the identification and documentation of each code fragment and reason for their existence. For an interpreted monitor, like the Streamlab framework, it is unfeasible to show this property.

Recent work introduces a hardware-based approach, compiling VHDL code out of an RTLola specification. This VHDL code can then be synthesized into an FPGA implementation. This thesis presents a prototype implementation of this compilation concerning a traceable result. It additionally describes the integration of a synthesized monitor into the unmanned aerial vehicle superARTIS by the German Aerospace Center (DLR).

#### Acknowledgements

First, I wish to thank my supervisor Bernd Finkbeiner for giving me student research assistant jobs, which lead to this thesis. Moreover, I would like to thank the Unmanned System Department at the German Aerospace Center (DLR) Institute of Flight Systems in Brunswick for giving me the chance to write this thesis based on our cooperation. Further, I thank my advisor Maximilian Schwenger not only for his support during the thesis but also for advising my work as a student research assistant. He gave me excellent guidance and constructive feedback over the last two years. I am especially thankful that he always pushed me to become better in writing and never giving up. Another grateful thanks to my advisor Sebastian Schirmer for his enthusiasm towards monitoring. He always found time to support me. Thanks to him, my time in Brunswick was very exciting with a lot of work, but always with a smile on my face. Moreover, I would like to thank all DLR employees for their support, especially Nikolaus Ammann and Christoph Torens. Furthermore, I want to thank Prof. Finkbeiner and Prof. Levedag, for reviewing this thesis. Last but not least, I would like to thank my family and friends for their ongoing support, with special thanks to Tom Baumeister, Niklas Metzger, and Christian Schön for proofreading this thesis.

#### Eidesstattliche Erklärung

Ich erkläre hiermit an Eides Statt, dass ich die vorliegende Arbeit selbständig verfasst und keine anderen als die angegebenen Quellen und Hilfsmittel verwendet habe.

#### Statement in Lieu of an Oath

I hereby confirm that I have written this thesis on my own and that I have not used any other media or materials than the ones referred to in this thesis.

#### Einverständniserklärung

Ich bin damit einverstanden, dass meine (bestandene) Arbeit in beiden Versionen in die Bibliothek der Informatik aufgenommen und damit veröffentlicht wird.

#### **Declaration of Consent**

I agree to make both versions of my thesis (with a passing grade) accessible to the public by having them added to the library of the Computer Science Department.

Saarbrücken, 10 February, 2020

## **Contents**

| 1. | Intro | ductio  | n                                      | 1    |

|----|-------|---------|----------------------------------------|------|

| 2. | Rela  | ted Wo  | ork                                    | 5    |

| 3. | Back  | kgroun( | d                                      | 7    |

|    | 3.1.  | The sp  | ecification language RTLola            | . 7  |

|    |       | 3.1.1.  | Concrete Syntax & Abstract Syntax Tree | . 7  |

|    |       | 3.1.2.  | Dependency Graph                       | . 10 |

|    |       |         | Type System                            |      |

|    |       |         | Finite Memory Monitoring               |      |

|    | 3.2.  |         | vare Compilation                       |      |

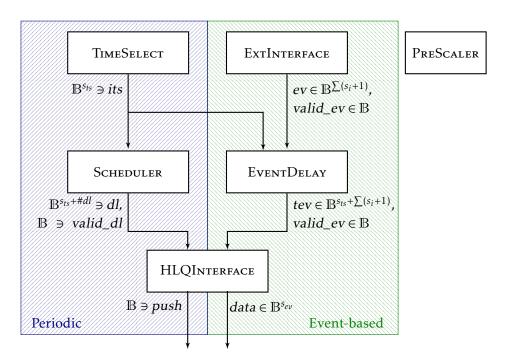

|    |       |         | General Structure                      |      |

|    |       | 3.2.2.  | Notation                               | . 34 |

|    |       | 3.2.3.  | High-level Controller                  | . 35 |

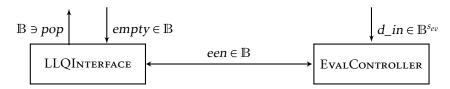

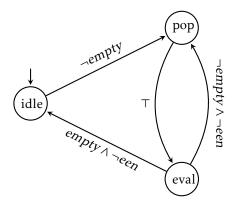

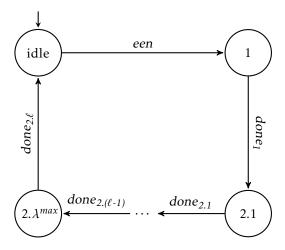

|    |       | 3.2.4.  | Low-level Controller                   |      |

|    | 3.3.  | VHDL    | & FPGA                                 | . 48 |

|    |       | 3.3.1.  | VHDL Example                           | . 48 |

|    |       |         | FPGA                                   |      |

| 4. | Prot  | otype   |                                        | 53   |

|    |       |         | Structure                              | . 55 |

|    |       |         | ation of Stream Types                  |      |

|    |       |         | Level Controller                       |      |

|    |       | _       | TimeSelect                             |      |

|    |       | 4.3.2.  | The Scheduler Template                 | . 59 |

|    |       | 4.3.3.  | CheckNewInput                          |      |

|    |       | 4.3.4.  | ExtInterface                           |      |

|    |       | 4.3.5.  | EventDelay                             |      |

|    |       | 4.3.6.  | HLQInterface                           |      |

|    |       | 4.3.7.  | High-level Controller                  |      |

|    | 4.4. | Low-L   | evel Controller .  |             |       |      |   | <br> | <br> | <br> | <br> | 67  |

|----|------|---------|--------------------|-------------|-------|------|---|------|------|------|------|-----|

|    |      |         | Input Streams .    |             |       |      |   |      |      |      |      |     |

|    |      | 4.4.2.  | Output Streams     |             |       |      |   | <br> | <br> | <br> | <br> | 69  |

|    |      |         | Sliding Windows    |             |       |      |   |      |      |      |      |     |

|    |      | 4.4.4.  | Evaluator          |             |       |      |   | <br> | <br> | <br> | <br> | 78  |

|    |      | 4.4.5.  | Low-level Contro   | ller        |       |      |   | <br> | <br> | <br> | <br> | 82  |

|    | 4.5. | Monito  | or                 |             |       |      |   | <br> | <br> |      |      | 83  |

| 5. | Inte | gration |                    |             |       |      |   |      |      |      |      | 85  |

|    |      | _       | ission             |             |       |      |   | <br> | <br> |      | <br> | 85  |

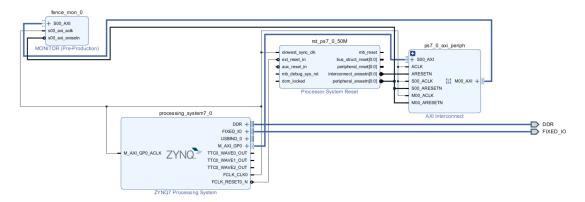

|    | 5.2. | Integra | ntion Setup        |             |       |      |   | <br> | <br> | <br> | <br> | 87  |

|    |      | U       | Setup              |             |       |      |   |      |      |      |      |     |

| 6. | Case | e Study |                    |             |       |      |   |      |      |      |      | 93  |

|    |      | -       | A Specifications . |             |       |      |   | <br> | <br> |      | <br> |     |

|    |      |         | Geofencing         |             |       |      |   |      |      |      |      |     |

|    |      | 6.1.2.  | -                  |             |       |      |   |      |      |      |      |     |

|    |      | 6.1.3.  | Cross Validation   |             |       |      |   |      |      |      |      |     |

|    | 6.2. |         | tion               |             |       |      |   |      |      |      |      |     |

|    |      |         | Static Analysis .  |             |       |      |   |      |      |      |      |     |

|    |      |         | Validation         |             |       |      |   |      |      |      |      |     |

| 7. | Con  | clusion | & Future Work      |             |       |      |   |      |      |      |      | 113 |

| A. | App  | endix   |                    |             |       |      |   |      |      |      |      | 115 |

|    |      |         | nce Rules Type Sys | tem         |       |      |   | <br> | <br> | <br> | <br> | 115 |

|    |      |         | ates               |             |       |      |   |      |      |      |      |     |

|    |      | -       | TIMESELECT         |             |       |      |   |      |      |      |      |     |

|    |      |         | CHECKNEWINPUT      |             |       |      |   |      |      |      |      |     |

|    |      |         | ExtInterface .     |             |       |      |   |      |      |      |      |     |

|    |      |         | HLC                |             |       |      |   |      |      |      |      |     |

|    |      | A.2.5.  | LLQINTERFACE .     |             |       |      |   | <br> | <br> | <br> | <br> | 118 |

|    | A.3. | Realiza | ation of Stream Ex | pressions   |       |      |   | <br> | <br> | <br> | <br> | 119 |

|    |      | A.3.1.  | Sliding Window I   | Realization | ıs .  |      |   | <br> | <br> | <br> | <br> | 125 |

|    | A.4. | Roadm   | ap to Integrate th | e monitor   | in Vi | vado | ) | <br> | <br> | <br> | <br> | 128 |

|    |      |         | ice                |             |       |      |   |      |      |      |      |     |

|    |      |         | Analyzes           |             |       |      |   |      |      |      |      |     |

|    |      | A.6.1.  | Cross Validation   |             |       |      |   | <br> | <br> | <br> | <br> | 136 |

|    |      |         | Sonsor Walidation  |             |       |      |   |      |      |      |      |     |

## Introduction

There are several ideas to use unmanned aircraft vehicles (UAV) for industrial applications, e.g., transport and reconnaissance, where these systems should fly autonomously. Due to the safety-critical aspect of aircraft, unexpected behavior of the autonomous system such as changing the computed flight path can result in a catastrophe. Therefore aviation companies have to ensure that their autonomous systems do not violate any critical constraints.

One approach to check the correctness of cyber-physical systems, i.e., systems that interact with the environment, is testing. Testing does not cover every possible behavior of the system, such that the absence of bad behavior cannot be guaranteed. Thus in safety-critical areas, stronger methods are needed. This goal can be reached with static verification methods like model checking. Model checking requires a model of the system and analyzes all possible runs in this model against a defined property afterward. If every path satisfies the specification, the absence of bad behavior, covered by the model and the specification, during the execution of the system is also verified. However, with increasing autonomy, the complexity of these systems increases dramatically. Therefore the size of the model also increases, such that these approaches might not be applicable.

In this thesis, we solve this issue with runtime monitoring [1, 2, 3, 4], a dynamic verification technique. In runtime monitoring, the behavior of the system is specified similar to model checking, but only the current run is analyzed, which reduces the complexity of the verification process. The idea of runtime monitoring is not to prevent bad behavior but to detect it and trigger an alarm to initiate countermeasures. This method can be applied either online or offline. In online monitoring, a separate monitoring component runs during the execution of the monitored system and analyses incoming data. In offline monitoring, the system produces a log file, which the monitor analyzes afterward.

To obtain formal guarantees on the behavior of the system, we need a formal specification language, e.g. temporal logic [5, 6, 7, 8]. A temporal logic consists of atomic propositions to express the current system state in an abstract way as well as boolean

and temporal connectives. Another type of specification languages are stream-based specification languages [9, 10, 11]. In comparison to temporal logics, such specifications are written data orientated like programming languages instead of logic orientated. In this thesis, we use the stream-based specification language RTLola [12], which is capable of expressing complex real-time constraints. Additionally, the monitor also provides formal guarantees and analyses, e.g. an upper bound on the memory consumption, as opposed to programming languages.

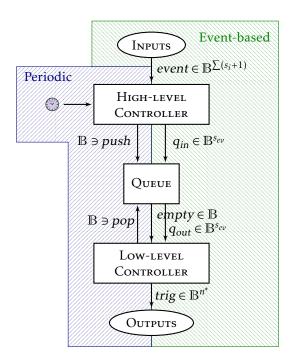

Incoming sensor data is defined as input streams in RTLola. This input data can then be combined into output streams to get statistical information. The specification language differentiates between event-driven output streams and periodic output streams, which differ in the so-called activation condition, i.e. the mechanism that initiates the update of a stream. As an example, to compute the average velocity during a complete run of an aircraft, the specifier defines an event-driven output stream that updates its value when the monitor receives a new velocity value. However, to compute the average velocity every 10s, a periodic-stream is needed. This stream evaluates its value with a frequency of 0.1Hz independent of the number of received new values. To express a violation, RTLola uses triggers that consist of a boolean expression and a message that raises the alarm when appropriate. The underlying framework StreamLab [13] receives an RTLola specification, analyses it and interprets the received input values based on the specification.

The current implementation of StreamLab is not applicable to safety-critical domains in the industry. As an example, we again consider aviation. To integrate hardware or software into aircraft, a certification process has to be passed. Part of this certification process is to connect the abstract specification with the concrete realization. For this connection, code fragments in the realization have to be annotated to relate them with their corresponding parts in the specification. However, the current StreamLab backend is an interpreter and not a compiler. In an interpreter, the input specification is encoded as data. Such data fragments are generated dynamically and cannot be annotated statically, which is demanded by the certification process. To solve this issue, we have to consider the specification as arbitrary, but fix in the annotation process. However, connecting the specification and the realization with such a representation is not as distinct as considering a specific specification. This challenges the annotation process and would be too costly in practice. In comparison, a compilation takes as input solely a specification and compiles a realization that can only monitor the incoming specification. This compiled monitor contains for each stream code fragments instead of data fragments. With these input specific code fragments, the relationship between a concrete specification and its corresponding code fragments can now be described.

Recent work [14] introduces a compilation from an RTLola specification to the Very High-Speed Integrated Circuit Hardware Description Language (VHDL) [15], which can then be synthesized into a Field Programmable Gate Array (FPGA). One advantage of a hardware-based solution is the parallel computation of different stream values without producing an overhead in comparison to a software-based solution. Another

important criterion for using hardware is the reduced power consumption that is limited in embedded systems.

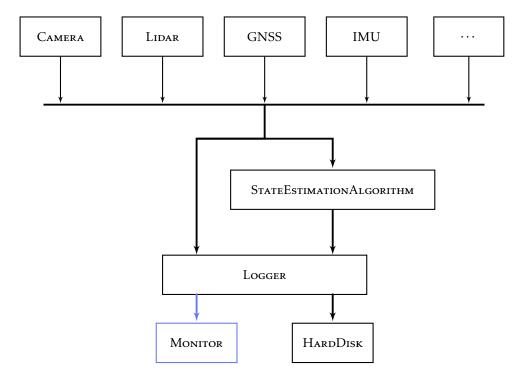

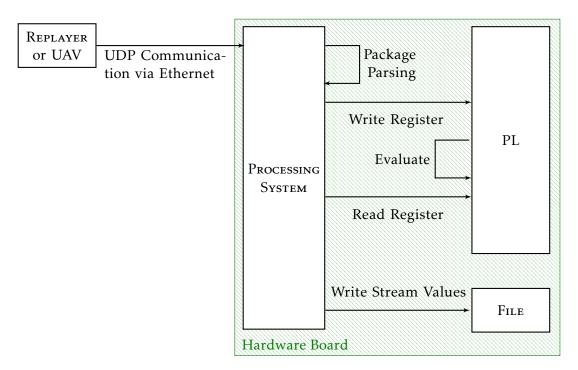

This thesis describes a prototype implementation based on the theory for a hardware-based monitor, compiling an RTLola specification to VHDL code. Additionally, the compilation identifies and documents the code fragments concerning the specification, moving forward in the certification process. To test the real-world application of the monitor, we integrate our prototype into the Autonomous Rotorcraft Testbed for Intelligent Systems (ARTIS)<sup>1</sup> to monitor UAVs. This system is used for the development and evaluation of components for an autonomous flight system from the German Aerospace Center (DLR). It consists of a software framework to simulate the flight of a UAV as well as a fleet of unmanned aircraft. First, we integrated the monitor in the hardware-in-the-loop flight simulation that replays a flight based on log files. Next, we integrate the monitor on the superARTIS UAV to monitor the system during an actual flight. This integration results in a case study of monitoring UAVs with the specification language RTLola using FPGAs.

<sup>1</sup>https://www.dlr.de/ft/en/desktopdefault.aspx/tabid-1387/1915\_read-15851/

Chapter 2

### Related Work

To use formal runtime verification, we need a formal specification language. One approach is temporal logic [5, 6] consisting of atomic propositions, boolean arithmetic, and temporal operators. The constructed monitoring tools reach from inline methods to outline methods. The first approach adds assertions in the monitored system based on the specification. The second one constructs the monitor as a separate component out of the specification. One of these approaches is P2V [16] that compiles assertions written in the specification language sPSL [17] to synthesizable Verilog code. Another construction for a hardware-based monitor with temporal logic is introduced by Finkbeiner and Kuhtz [18], to monitor LTL specifications that can have unbounded future constraints with an FPGA implementation. The development of real-time temporal logics such as metric temporal logic (MTL) [7] and signal temporal logic (STL) [8] affected the engineering of new monitoring tools, e.g. Jaksic et al. [8] introduce an FPGA monitor that can express real-time constraints with STL. These new logics have the advantage of expressing timing behavior with real-time values instead of discrete ones. However, one drawback when monitoring systems with temporal logics is their expressiveness. With temporal logics, it is only possible to express the satisfaction or the validation of a property which is often not sufficient when monitoring cyber-physical systems, e.g. the time of the invalidation may not be the time of the system failure. To cover this problem, Moosbrugger et al. [19, 20] introduced the monitoring tool R2U2, which uses not only MTL to detect a validation of a property but also Bayesian networks to reason about the failure.

Another approach to increase the expressiveness but still have formal guarantees are stream-based specification languages. In stream-based specification languages, the user declares input streams, representing the input data, and output streams that contain calculations like arithmetic expressions but also future or past offsets to access future and past values. Because stream-based specification languages like Lola [10], Lustre [9, 21] or Copilot [11] were initially developed to monitor digital circuits, they assume that all input data is received synchronously, i.e., each input stream receives a new

value at the time, which is the case in circuits. However, this assumption does not hold when monitoring cyber-physical systems in general and restricts the expressiveness of the described properties. New approaches like RTLola [12], based on Lola, covers this problem by receiving input events with a non-fix rate, e.g. inputs are received without a fixed frequency. RTLola also introduces real-time features to Lola, like adding a frequency to output streams, describing the period when the value of an output stream should be computed, or the aggregation of streams over a specified period. Another extension of Lola to handle asynchronous event streams and to describe real-time properties is TeSSLa [22]. TeSSLa is a monitoring tool that reconstructs the program flow of a C program by receiving events from the embedded trace unit of the microprocessor and monitors this reconstruction. In comparison to RTLola, this requires information about the program flow of the monitored software when writing the specification. Besides, TeSSLa cannot aggregate over a stream for a specified period. A further extension of Lola is Striver [23]. Striver handles asynchronicity of streams by annotations, describing the period when a value is updated. In comparison to RTLOLA, they do not provide a mechanism to access a value from a fixed-rate stream in streams that have a variable-rate. RTLOLA realizes this by sliding windows and the sample-and-hold operator.

Adolf et al. [24] integrated Lola into an unmanned aerial vehicle (UAV) similarly to our approach. They described real-time constraints with discrete time stamps and the current system time, e.g. the property that the frequency of the incoming data is in the given bound. The main difference to our approach is the new specification language RTLola. RTLola enables us to express more complex real-time properties and to express the current ones in a more elegant way. Another difference is the resulting monitor, which is, in our case, hardware-based and not software-based. An integration of a hardware-based runtime monitor in a UAV is described by Moosbrugger et al. [19]. They integrated their runtime monitoring tool R2U2 synthesized onto an FPGA in the NASA DragonEye. As specifications, they introduce monitors to check the integrity of the system but also specifications to recognize hacking attacks at the UAV. The main difference to our approach is that the R2U2 tool uses temporal logic instead of a stream-based specification language.

## **Background**

This chapter describes the general structure of the specification language RTLola, its hardware-based realization, and introduces the hardware description language VHDL.

#### 3.1. The specification language RTLOLA

In this thesis, we use RTLola [12] to describe properties in a formal way. RTLola introduces asynchronous monitoring and real-time constraints to the stream-based specification language Lola [10]. The following section first describes the concrete syntax of "vanilla" RTLola, the specification RTLola without any syntactical sugar such as infix notation for arithmetical operators. Then, we describe the transformation from the concrete syntax to an abstract syntax tree (AST). From this AST, we perform static analysis, i.e. a type checking analyzes. Afterward, we take a closer look at the semantics of the specification language.

All definitions, lemmas, and propositions are introduced and proven by Schwenger [25].

#### 3.1.1. Concrete Syntax & Abstract Syntax Tree

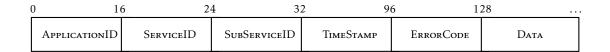

The formal semantics of RTLola is defined on the abstract representation of specification. For this reason, the function AST transforms the concrete syntax of a specification to an abstract syntax tree (AST), with  $s_n^{\downarrow} + s_n^{\uparrow} + s_n^{!}$  children. Note that from this point on, we uses marker to indicate the category of a stream. Input streams are symbolized with a down arrow  $(s_s^{\downarrow})$ , output streams with an up arrow  $(s_s^{\uparrow})$ , and trigger with an exclamation mark  $(s_s^{\downarrow})$ . To indicate that a stream can be either an input stream or output stream, we use a vertical line  $(s_s^{-})$ . The following paragraphs describe the concrete and abstract syntax for input streams, output streams, and triggers.

The  $i^{th}$  input stream  $s_i^{\downarrow}$  is defined by:

```

input a: T

```

The output of the AST function for input streams is  $s_i^{\downarrow} = (a, AST(T))$ . The name a of the stream is irrelevant for the formal semantics, but needed in the realization. However, the type T needs to be transformed into an AST object. For readability, we define  $s_i^{\downarrow}.name := a \text{ and } T_i^{\downarrow} := AST(T).$ The  $j^{th}$  output stream  $s_j^{\uparrow}$  is defined by

```

output a: T @nHz := expr

```

This syntax is similar to input streams, but introduces two more components: the evaluation frequency @nHz and the expression expr. The AST representation for output streams is  $s_s^{\uparrow} = (a, AST(T), n, AST(expr))$ , and respectively  $s_j^{\uparrow}.name := a$ ,  $T_j^{\uparrow} := AST(T)$ ,  $s_j^{\uparrow}.ext := n$ , and  $s_j^{\uparrow}.expr := AST(e)$ . We restrict the frequency to a positive natural number  $\dot{n}$  with unit Hertz. The resulting monitor and the specification language is theoretically capable of working with other positive rational numbers and other time units. However, for simplicity reasons in the semantics, we perform theses restrictions.

The specified frequency in output streams is an optional value. The following concrete syntax for an output stream with the AST representation  $s_s^{\uparrow} = (a, AST(T), \bot, AST(e))$  is also possible:

```

output a: T := expr

The k^{th} trigger s_k^! is defined by:

trigger a "msg"

```

Trigger contain a stream name a and a message msg. The AST transforms the name to the corresponding stream reference if the name is specified and to  $\bot$  otherwise. This transformation results in the following AST representation, with  $s_k^! . tar := s$  and  $s_k^!.msg := msg$ :

$$s_{k}^{!} = (s, msg) = \begin{cases} (s_{j}^{\uparrow}, msg) & \text{if } s_{j}^{\uparrow}.name = a \\ (\bot, msg) & \text{otherwise} \end{cases}$$

#### Expressions

RTLola supports different computation rules for output streams. For each expression, we define the concrete syntax and the abstract representation as output of the AST function, starting with different accesses:

Synchronous Lookup: The expression s accesses the current stream value of s and bounds the timing of the accessor stream to the schedule of the accessed stream. The abstract representation for this expression stores a reference to the accessed

$$AST(s) := \begin{cases} Sync(s_i^-) & \text{if } s_i^-.name = s \\ Sync(\bot) & \text{otherwise} \end{cases}$$

Sample & Hold Lookup: The concrete syntax for the sample & hold lookups is defined by: s.hold(). Sample & hold lookups access the current stream value of s as synchronous lookups. However, these lookups are considered asynchronous, i.e. the timing of the accessor stream is not bounded to the schedule of the accessed stream. The abstract representation for this expression also stores a reference to the accessed stream, resulting in:

$$AST(s.hold()) := \begin{cases} Hold(s_i^-) & \text{if } s_i^-.name = s \\ Hold(\bot) & \text{otherwise} \end{cases}$$

Offset Lookup: Offset expressions e.offset(by: -n) correspond to synchronous lookup accessing not the current, but the  $n^{th}$  previous value. Like synchronous lookups, the timing of the accessor stream is also bounded to the schedule of the accessed stream. This expression results in the following abstract representation storing the offset number n besides the stream reference and the access category:

$$AST(\texttt{s.offset(by:-n)}) := \begin{cases} Offset(s_i^-, n) & \text{if } s_i^-.name = s \\ Offset(\bot, n) & \text{otherwise} \end{cases}$$

Sliding Window Lookup: Sliding windows s.aggregate(over:  $\delta$ s, using:  $\gamma$ ) aggregate over all values inside a real-time duration  $\delta$  with an aggregation function  $\gamma$ . These timed accesses are asynchronous and do not influence the timing behavior of the accessor stream, as Sample & Hold lookups. The abstract representation contains therefore the stream reference, the time duration and the aggregation function:

$$AST(\texttt{s.aggregate}(\texttt{over:}\delta\texttt{s}, \texttt{using:}\gamma)) \coloneqq \begin{cases} \textit{Window}(s_i^-, \delta, \gamma) & \text{if } s_i^-.name = s \\ \textit{Window}(\bot, \delta, \gamma) & \text{otherwise} \end{cases}$$

Default Expression: Because some lookups can fail, the return type of sample & hold, offset, and sliding window lookups are optional types. RTLola uses default expressions e.defaults(to: e) returning the default value in case of a lookup fail. This results in the abstract interpretation:

$$AST(e.defaults(to: d)) := Default(AST(d), AST(e))$$

Function Expression: Function expressions f(e1,...,en) are used to refine the received input data. RTLola supports the usual operators with the infix notation, such as constants, arithmetic operations, or conditionals encoded as n-ary functions. Note that, because we encode the common condition if cond then cons else alt as a ternary function, we evaluate this expression without side effects. Additionally,

RTLola implements the functions for the absolute value or the square root. The abstract representation is given by:

$$AST(f(e1,...,en)) := Func(f,AST(e1),...,AST(en))$$

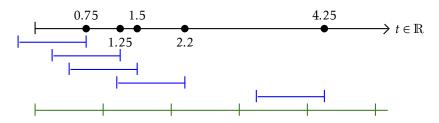

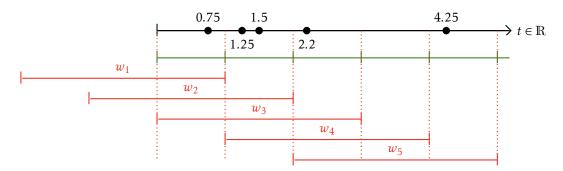

Note that for sliding windows as well as for streams, we assign each sliding window to a unique identifier. Therefore, the  $l^{th}$  sliding window in the specification is identified by  $w_l$ .

The first constraint for a valid RTLola specification is the syntactical validity:

**Definition 1** (Syntactic Validity [25])

An RTLola specification is syntactically valid iff

- all stream and trigger definitions conform to the concrete syntax stated above.

- AST(s) can be computed without violating a condition. This especially includes

that all stream names can be resolved, such that no ⊥ value is contained in the

AST.

- all names of streams are unique, i.e.,  $\forall i, j : s_i^-$ .  $name = s_i^-$ .  $name \implies i = j$ .

Before we start with the constraints for semantical validity, we introduce some further notation. We denote  $n^{\downarrow}$  as the number of input streams,  $n^{\uparrow}$  the number of output streams,  $n^{!}$  the number of trigger, and  $n^{w}$  the number of sliding windows. Additionally, we call the set of all input streams in a specification  $Stream^{\downarrow}$ , the set of all output streams  $Stream^{\uparrow}$ , the set of all triggers  $Stream^{!}$ , and the set of all streams Stream. The set W defines the set with all sliding windows. These sets are defined with:

```

Stream^{\downarrow} = \{s_{i}^{\downarrow} \mid i \leq n^{\downarrow}\}

Stream^{\uparrow} = \{s_{i}^{\uparrow} \mid i \leq n^{\uparrow}\}

Stream' = \{s_{i}^{\downarrow} \mid i \leq n^{\downarrow}\}

Stream = Stream^{\downarrow} \dot{\cup} Stream^{\uparrow} \dot{\cup} Stream'

W = \{w_{i} \mid i \leq n^{w}\}

```

In this chapter, we refer from this point in time to the AST instead of the concrete syntax.

#### 3.1.2. Dependency Graph

The previous section defined the syntactical validity of a specification. Before we can build a monitor out of the specification, we need to define the semantical validity. Section 3.1.1 introduced different stream accesses occurring in the stream expression. RTLola uses the definition of a dependency graph (DG) to describe the dependencies

**Def.** Syntactic Validity

between streams. Then, the DG is used for semantic checks like the type analysis or the existence of an evaluation model. Additionally, we determine from the DG a static memory upper bound for each stream. These upper bounds are used from the compiler to determine the number of registers in the monitor realization.

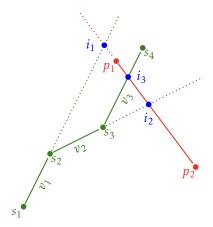

RTLola builds the DG from the AST by iteration over it. We describe a dependency as a triple consisting of the source stream, the weight, and the target stream. The weight of a dependency is either the offset which value needs to be addressed, or a pair with the duration and aggregation function for sliding windows. The dependencies for an output stream  $s_i^{\uparrow}$  is computed recursively from the stream expression. With these dependencies, RTLola builds the dependency graph.

#### **Definition 2** (Dependency Graph [25])

The dependency graph of a specification is a directed multi-graph DG = (V, E) with weighted edges. Its vertices are streams and the edges reflect dependencies between streams:

**Def.** Dependency Graph

$$V := Stream$$

$$E := \bigcup_{1 \le i \le n^{\uparrow}} dep_{s_i^{\uparrow}}(s_i^{\uparrow}.expr) \cup \bigcup_{1 \le i \le n^{\downarrow}} \{(s_i^{\downarrow}, 0, s_i^{\downarrow}.tar)\}$$

The function  $dep_{s_i^{\uparrow}}$  is defined as:

$$\begin{split} dep_{s_i^\uparrow}(Offset(s_j^-,n)) &\coloneqq \{(s_i^\uparrow,n,s_j^-)\} \\ dep_{s_i^\uparrow}(Default(e,e')) &\coloneqq dep(e) \cup dep(e') \\ dep_{s_i^\uparrow}(Func(f,a_1,\ldots,a_n)) &\coloneqq \bigcup_{0 < i \leq n} dep(a_i) \\ dep_{s_i^\uparrow}(Sync(s_j^-)) &\coloneqq \{(s_i^\uparrow,0,s_i^-)\} \\ dep_{s_i^\uparrow}(Hold(s_j^-)) &\coloneqq \{(s_i^\uparrow,0,s_j^-)\} \\ dep_{s_i^\uparrow}(Window(s_i^-,\delta,\gamma)) &\coloneqq \{(s_i^\uparrow,(\delta,\gamma),s_j^-)\} \end{split}$$

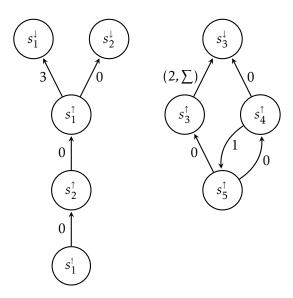

Figure 3.1.: Dependency Graph for the specification in Example 3.1.1.

**Example 3.1.1.** Figure 3.1 represents the dependency graph for the following specification:

```

input a : Float32

input b : Float32

input c : Int64

output d : Float32 := a.offset(by: -3).defaults(to: 0.0) + b

output e : Bool := d < 40.5

output f : Int64 @1Hz := c.aggregate(over: 4s, using: ∑)

output g : Int64 := c * h.offset(by: -1).defaults(to: -4)

output h : Int64 := f.hold().defaults(to: 50) - g

trigger e "e is smaller than 40.5"</pre>

```

Input streams do not access other stream and are always sink nodes. Whereas trigger are always leaves nodes, because they cannot be accessed by other streams. The dependencies of output streams is defined by their lookups in the stream expression. The output stream d for example has an offset lookup to the input stream a and a synchronous lookup to the input stream b. Therefore, the dependency graph has a 3-weighted edge from  $s_1^{\uparrow}$  to  $s_2^{\downarrow}$ , and a 0-weighted edge from  $s_1^{\uparrow}$  to  $s_2^{\downarrow}$ .

#### **Evaluation Models**

With the DG, we start with the first semantical analysis for a RTLola specification without knowing the concrete semantics. RTLola uses an evaluation model to describe the relation between input and output streams in the semantics. Because the formal definition of an evaluation model is not needed to check the semantical validity, we just give an intuitive definition: An *evaluation model* of a specification is a set of infinite sequences, one for each stream. To get an intuition for an evaluation model, consider the following specification:

**Evaluation Model**

```

input a : Int8

output b : Int8 := a + 1

```

The specification evaluates the output stream b to the value from input a plus 1. Intuitively, the unique evaluation model for this specification follows the specification and adds one to the input value. Formally, this is described by:

```

\{(s_a^{\downarrow}, x), (s_h^{\uparrow}, y) \mid x, y, z \in \mathbb{N}^{\omega} \land x_i = (z_i \bmod{128}) \land y_i = (z_i + 1 \bmod{128})\}

```

However, there are specifications which have more than one valid evaluation model like:

```

output a : Int8 := a

```

This specification consists only of one output stream, which assigns the output stream a to the value of a. This specification is syntactically valid, but we can find different evaluation models. One possible model is similar to the first part of the previous example. The model assigns a to each value inside the modulo class. Another model, which assigns a to a constant value c, is also possible. Formally, we can describe these models as:

- $\{(s_a^{\downarrow}, x) \mid x, z \in \mathbb{N}^{\omega} \land x_i = (z_i \bmod 128)\}$

- $\{(s_a^{\downarrow}, x) \mid x \in \mathbb{N}^{\omega} \land c \in \mathbb{N} \land x_i = c\}$

Another possibility for a syntactically valid specification is the absence of an evaluation model. Consider the following specification:

```

output a : Int8 := b

output b : Int8 := a + 1

```

In this example, the value of a is assigned to the value of b, and b to a plus 1. Because of the circular dependency, we cannot find two sequences fulfilling the specification. To guarantee that the monitor provides exactly one evaluation model such that for the same input sequences the monitor computes the same output sequences, the definition of well-definedness was introduced for Lola.

```

Definition 3 (Well-definedness [10])

```

A specification is said to be well-defined if a unique model exists.

**Def.** Well Definedness

To check the existence of a unique evaluation model for a specification, Lola checks the specification for well-formedness:

```

Definition 4 (Well-formedness [10])

```

A Lola specification is *well-formed* if there is no 0-weighted cycle in the dependency graph.

**Det.** Well-formedness

The proof of the following theorem confirms that well-formedness is a sufficient but no necessary criterium.

**Theorem 1** (Unique Evaluation Model [10]). A specification has a unique evaluation model if the specification is well-formed. The inverse direction does not hold.

The intuitive explanation for the correctness of this theorem results from an order of the stream, which can be determined with the absence of a 0-cycle. This order describes the schedule of the stream evaluation and is described in the next section more detailed. An example for the inverse is presented by the following stream:

```

output a : Bool := a ∨ ¬a

```

The unique evaluation model for this stream is a sequence which always returns true. However, the dependency graph has a 0-edge from the stream a to itself, resulting in a 0-weighted cycle.

To adapt this theorem to RTLola, we need to consider the asynchronous lookups sample & hold and sliding window. In both cases, the expression requires access to the target stream. We first look at their representations in the DG. Sample & hold lookups are represented as synchronous accesses, with a 0-weight edge. The difference between these lookups is the timing of their evaluation. However, this is irrelevant for the dependency description, so they are treated in the same way. Sliding windows are represented by the duration of the window and the aggregation function. The computation of the sliding window requires an iterative lookup on the current value of the target stream. For the evaluation model, the number of accesses is irrelevant as long as only the current value is accessed. So we treat sliding window lookups as 0-weight edges. With these adaptions, RTLola uses the same definitions for well-formedness. The proof for this adaption and the resulting theorem is presented by Schwenger [25].

**Example 3.1.2** (Well-formedness). Consider again the dependency graph from Figure 3.1. This graph contains only one cycle between  $s_4^{\uparrow}$  and  $s_5^{\uparrow}$ , which a weight of one. So the dependency graph has no 0-weighted cycle, and the specification is well-formed.  $\triangle$

#### **Evaluation Order**

To prove the existence of a unique evaluation model, RTLola computes an evaluation order from the DG. This order describes the schedule of the stream evaluations. To motivate the defined evaluation order and to get an intuition, we discuss at first two examples.

**Example 3.1.3.** The following specification declares one input stream a and two output streams b and c. During the evaluation b adds up the constant number 3 to the input value. The output stream c then adds up the current value of b to the previous one.

```

input a : Int8

output b : Int8 := a + 3

output c : Int8 := b + b.offset(by:-1).defaults(to: 0)

```

The input stream a is synchronously accessed by the output stream b, such that a needs to be evaluated before b. The output stream c accesses the current value and the previous one of b synchronously. For this reason, the output stream c evaluates the stream expression after b. These accesses result intuitively in the order a < b < c.  $\triangle$

#### **Example 3.1.4.** Consider the following specification:

```

input a : Int8

output b : Int8 := a + c.offset(by:-1).defaults(to: 0)

output c : Int8 := b + b.offset(by:-1).defaults(to: 0)

```

Compared to the previous example, the specification adapted the stream expression of output stream b to add up a with the previous value of c. Using the same approach as in the previous example results in the following problem. Because b accesses c and c is accessed by b, we cannot define a total order in the same way. Because b accesses the previous value, which is already available without a computation of c, b can theoretically compute the stream expression before c. However, if we evaluate b before c a new problem arises. Since c was not updated yet, the stream offset lookup in b accesses the second last value and not the previous one as intended.

This issue is solved with a new evaluation phase — called *pseudo evaluation phase*. This phase assigns the current value of each output stream, which will be evaluated, to a pseudo value. With this assignment, we shift the offset values to their correct position such that the stream expressions using the offset values can compute their stream expressions. In our example, with this shift, we can evaluate b after the synchronous direct access stream a was evaluated, and c after b. RTLola replaces the pseudo value with the correct one, when the stream is evaluated based on the evaluation order.

Pseudo Evaluation Phase

RTLola uses the dependency graph to receive the evaluation order for a specification. Because the pseudo evaluation phase covers the offset lookups such that offset values are at their intended position, the computation only considers 0-weight edges and sliding windows. Intuitively, if a stream  $s_i^{\uparrow}$  has a direct access to stream  $s_j^{-}$ , it needs to be evaluated before  $s_i^{\uparrow}$ . This intuition results in the following definition:

#### **Definition 5** (Evaluation Order [25])

The *evaluation order*  $\prec$  is a partial order on streams, reflecting the structure of the dependency graph DG = (V, E). The evaluation order is the transitive closure of a relation satisfying the following rules:

**Def.** Evaluation Order

```

1. \forall i, j : s_i^{\downarrow} < s_j^{\uparrow}

```

2.

$$(s_i^{\uparrow}, x, s_j^{\lnot}) \in E \land (x = 0 \lor x = (\delta, \gamma)) \land s_i^{\uparrow} \neq s_j^{\lnot} \Longrightarrow s_j^{\lnot} \prec s_i^{\uparrow}$$

Intuitively, the first rule restricts the evaluation of input streams before the evaluation of output streams. This is in general not necessary but simplifies the evaluation. The last rule covers the previously mentioned dependencies between two streams.

**Remark 3.1.1.** The definition from Schwenger [25] contains three rules. In the previous definition, the rules correspond to the first and the third rule. In this thesis, we omit the second rule, covering the transitivity of the order. Because the definition already claims that the evaluation order is a partial order, this implicitly includes the constraints reflexivity, transitivity, and antisymmetry, such that the second rule is already covered.

The order between two streams, which are incomparable in the evaluation order, can be evaluated independently of each other, i.e. the order between those streams does not have an influence on the stream evaluation. These streams either do not depend on each other or all needed values are already accessible. Because trigger values are not accessed by output streams, triggers are not part of the evaluation order and are computed after all output streams.

The following proposition and the corresponding proof guarantees the existence of an evaluation order for well-formed specifications.

**Proposition 2** (Existence of Evaluation Order [25]). Every well-formed specification has an evaluation order.

The proof first constructs a relation out of the dependency graph with the constraints from Definition 5 and then proves that the reflexive transitive closure is a partial order. For readability, we introduce a new representation for the evaluation order.

**Definition 6** (Evaluation Layer [25])

The evaluation layer is an equivalent representation of  $\leq$ . If  $Layer(s_i^-) = k$  then there is a strictly decreasing sequence of k streams w.r.t.  $\prec$  starting in  $s_i^-$ .

For readability,  $\lambda^{max}$  describe the maximum layer of a specification, formally defined as:

$$\lambda^{max} := \max\{\lambda \mid \exists s_j^- \colon \lambda = Layer(s_j^-)\}$$

**Example 3.1.5** (Evaluation Layer). The specification from Example 3.1.1 results in the following evaluation layers:

$$Layer(s_1^{\downarrow}) = 0$$

$$Layer(s_2^{\uparrow}) = 2$$

$$Layer(s_3^{\downarrow}) = 0$$

$$Layer(s_3^{\downarrow}) = 1$$

$$Layer(s_1^{\uparrow}) = 1$$

$$Layer(s_5^{\uparrow}) = 2$$

Input streams are always in layer zero. The output streams d and f are on the first layer, because they depend only on the input streams. The output stream e has a synchronous lookup to the output stream d. For this reason, its layer is after the layer of e. The output stream g has a synchronous lookup to the input stream c and an offset lookup to g, which is irrelevant for the evaluation order. Therefore, its layer is the same layer as the layer of d and f. The layer of the output stream g is greater than the layer of f and g, because of the synchronous lookup and the sample & hold lookup.

Def. Evaluation Layer

→ Ex. 3.1.1, P. 11

#### 3.1.3. Type System

A type checking analysis is part of the semantical validity, finding inconsistencies in the stream evaluation. To find these inconsistencies, the concrete syntax demands that each stream is annotated with the corresponding type. However, most of the output stream types can be inferred from the stream expression, such that the realization does not have this restriction.

In RTLOLA, a type is a pair consisting of the *value type* and the *activation condition*. The value type defines the bit range and its interpretation of the stream values, i.e. the input and output values of the monitor. Possible representations are booleans, signed and unsigned integers, as well as floating point numbers. This enumeration results in the following definition:

**Definition 7** (Value Types [25])

In RTLola, a single value  $\tau$  is of one of the following types:

Def. Value Type

$$VT := \{Bool, Int(x), UInt(x), Float(y) \mid x \in \{8, 16, 32, 64\}, y \in \{16, 32, 64\}\}$$

**Remark 3.1.2.** In the original definition Float(16) is not mentioned. Because a specification is realized on hardware in this thesis, space is highly limited. Therefore, we introduce an additional floating type, with a smaller bit representation.

The activation condition of a stream defines the timing behavior, i.e. the condition when a stream needs to be updated. RTLola separates output streams into two categories, event-based and periodic, reflected in the activation condition. Periodic streams are annotated with a frequency, defining fixed time points, the stream is evaluated on. Event-based streams are streams without a frequency and therefore evaluate at arbitrary time points. The activation condition for theses streams is inferred from the stream expression. Therefore, we first collect all synchronous and offset lookups in the stream expressions. For this set, we then compute recursively all synchronous and offset lookups until we reach only a set of input streams. This resulting set then describes the activation condition. An output stream  $s_i^{\uparrow}$  with activation condition  $\iota$  is updated iff the incoming event updates *all* input streams  $s_i^{\downarrow} \in \iota$ .

#### **Definition 8** (Activation Condition [25])

In RTLola, an activation condition  $\sigma$  is either an element of an event type  $\iota \in ET$  or of a periodic type  $\pi \in PT$ . The set ET is defined as the powerset of all input streams in the specification, covering all possible input event combinations. The set PT is defined as the set of all time points where at least one periodic stream is evaluated. These sets are formally defined as:

**Def.** Activation Condition

$$ET := 2^{Stream^{\downarrow}}$$

$$PT := \left\{ p \mid p \in \mathbb{N} \land \left( \gcd(P^{spec}) \mid p \right) \land \left( p \mid \operatorname{lcm}(P^{spec}) \right) \right\}$$

The set  $P^{spec}$  is defined as the set of all periodic output streams:

$$P^{spec} := \bigcup_{s_i^\uparrow \in Stream^\uparrow} \{s_i^\uparrow.ext\}$$

**Remark 3.1.3.** The previous definition derivates from the original one. In this thesis, we define single pacing type instead of defining the event type ET and periodic type PT, which does not change the intended definition. Additionally, we use a different notation. The activation condition is defined as a single value of the pacing type, which is the set of activation conditions of a specification.

**Remark 3.1.4** (Periodic Input Streams). In RTLOLA, the activation condition of an input stream is always event-based. To show the problem of a periodic input stream, we assume a specification containing the stream: input a: Int8 @1Hz. To evaluate the input stream a the monitor demands fixed time steps, exactly every second, for an incoming event updating a. However, in this case the specification has control of the input streams, which is in practice not possible. Even if input values are produced with a fixed frequency, the frequency cannot be guaranteed for the monitor because of internal delays and interferences. Therefore, RTLOLA excludes periodic input streams.

**Remark 3.1.5.** To annotate the activation condition  $\iota$  of an event-based stream  $s^-$  in the specification, we use the following notation:  $s^ @\iota$ . Note that  $\iota$  is a set of input streams.

To get an intuition for the activation condition, consider the next example.

**Example 3.1.6** (Activation Condition). The following specification presents a fragment of the specification in Example 3.1.1:

```

input a : Float32 @{a}

input b : Float32 @{b}

input c : Int64 @{c}

output d : Float32 @{a,b} := a.offset(by: -3).defaults(to: 0.0) + b

output e : Bool @{a,b} := d < 40.5

output f : Int64 @1Hz := c.aggregate(over: 4s, using: ∑)</pre>

```

The input streams a, b, and c are event-based. The activation condition of input streams is always an event-based type with the input stream itself because they depend on no other streams. The activation condition of the event-based output stream d is bounded to the input streams a and b, because of the synchronous lookup and the offset lookup. In this example, the output stream d is updated iff the monitor receives an incoming event which updates a and b. The event-based output stream e has a synchronous lookup to the output stream d. Therefore, it recursively depends on the input streams a and b, resulting in the same activation condition. The periodic stream f is annotated with a frequency and is, for this reason, updated every second, independent on the number of received events.

→ Ex. 3.1.1, P. 11

From the AST, RTLola can assign each stream in the specification to a concrete type. However, to validate stream expressions we perform a type checking analysis. For this, we have to assign each expression to its corresponding type. Because expressions, in comparison to streams, are not annotated with their concrete types we have to infer them, resulting in a new problem. The following example visualizes this problem, assigning expressions to concrete types. Consider a constant expression 3, which can be a subexpression of  $s_i^- + 3$ . In case of  $T_i^- = Int(8)$ , the concrete type of 3 is Int(8). However, if  $s_i^-$  has type UInt(8), the concrete type of 3 is UInt(8). For this, the type of an expression is not a single concrete type, but a candidate set of concrete types. The resulting candidate set for 3 is  $\{Int(x), UInt(x) | x \in \{8, 16, 31, 64\}\}$ . The candidate set of an expression is defined as the *abstract type*. Like the concrete type, the abstract type is defined as a pair, storing the value type and the activation condition.

#### **Definition 9** (Abstract Types [25])

A single *abstract type*  $(\widetilde{\tau}, \widetilde{\sigma})$  is defined as an element of  $\widetilde{VT} \times (\widetilde{ET} \cup \widetilde{PT})$ , with:

**Def.** Abstract Type

$$\begin{split} \widetilde{VT} &:= \{\emptyset, \{Bool\}\} \\ & \cup \bigcup_{i=4}^{6} \{Float(y) \mid \{16, 32, 64\} \ni y \geq 2^{i}\} \\ & \cup \bigcup_{i=3}^{6} \{\{UInt(y) \mid \{8, 16, 32, 64\} \ni y \geq 2^{i}\}, \{Int(y) \mid \{8, 16, 32, 64\} \ni y \geq 2^{i}\}\} \\ \widetilde{ET} &:= ET \\ \widetilde{PT} &:= PT \end{split}$$

Intuitively, the abstract type is defined as:

- The single abstract value type  $\tilde{\tau}$  denoting the set of all possible values types.

- The single abstract periodic type  $\widetilde{\pi}$  denoting the maximal frequency of how the stream can be evaluated.

- The single abstract event type  $\tilde{\iota}$  denoting the minimal set of dependencies of the expression.

From now on, we use the tilde to differentiate concrete and abstract types. Additionally,  $\tau$  always references to the value type and  $\sigma$  the activation condition. Furthermore,  $\pi$  denotes a periodic type and  $\iota$  an event type.

#### Type Lattice

RTLola uses a type checker which ignores the details about the underlying type system. With this approach the type system can be extended or modified without changing the

model checking algorithm. Nevertheless, to make constraints about the type system, we use the concept of a meet-semi lattice.

**Definition 10** (Meet-semi Lattice)

A meet-semi lattice is a tuple  $(S, \sqcap)$  consisting of a set S, ordered by a partial order  $\leq$ , Def. Meet-semi and a binary relation  $\sqcap$ , with the following constraints:

- Existence of a greatest lower bound between two elements:  $\forall s_1, s_2 \in S. s_1 \sqcap s_2 \in S$

- Associativity of □

- Commutativity of □

- Reflexivity of  $\sqcap$

The underlying meet semi-lattice for the current type system is defined as:

**Definition 11** (Type Lattice [25])

The type system of RTLola is the meet-semilattice  $(\widetilde{VT} \cup Opt(\widetilde{VT}) \cup \widetilde{PT} \cup \widetilde{ET} \cup \{\bot\}, \sqcap)$ with the following meet operation:

$\widetilde{\tau_{1}} \sqcap \widetilde{\tau_{2}} := \begin{cases} \widetilde{\tau_{1}} \sqcap_{VT} \widetilde{\tau_{2}} & \text{if } \widetilde{\tau_{1}}, \widetilde{\tau_{2}} \in VT \\ Opt\langle \widetilde{\tau_{1}}' \sqcap_{VT} \widetilde{\tau_{2}} \rangle' & \text{if } Opt\langle \widetilde{\tau_{1}}' \rangle = \widetilde{\tau_{1}} \land Opt\langle \widetilde{\tau_{1}}' \rangle = \widetilde{\tau_{1}} \\ \widetilde{\tau_{1}} \sqcap_{PT} \widetilde{\tau_{2}} & \text{if } \widetilde{\tau_{1}}, \widetilde{\tau_{2}} \in PT \\ \widetilde{\tau_{1}} \sqcap_{ET} \widetilde{\tau_{2}} & \text{if } \widetilde{\tau_{1}}, \widetilde{\tau_{2}} \in ET \\ \bot & \text{otherwise} \end{cases}$

The single meet operators are defined as:

- $\widetilde{\tau}_1 \sqcap_{VT} \widetilde{\tau}_2 := \widetilde{\tau}_1 \cap \widetilde{\tau}_2$

- $\widetilde{\pi}_1 \sqcap_{PT} \widetilde{\pi}_2 := \gcd(\widetilde{\pi}_1, \widetilde{\pi}_2)$

- $\widetilde{\iota}_1 \sqcap_{FT} \widetilde{\iota}_2 := \widetilde{\iota}_1 \cup \widetilde{\iota}_2$

Intuitively, a meet operator usually refines two elements to a more concrete one. For this, the different meet operators have the following messages.

• An abstract value type contains all possible concrete value types. Therefore, the refinement of two abstract value types are all concrete types, which are contained on both sides. If the types are incomparable the meet operator returns  $\emptyset$ .

#### Def. Type System in RTLOLA

- An abstract periodic type is the maximal frequency on which the stream or expression can be evaluated. The result of the meet of two periodic types is the maximal frequency on which both streams can be evaluated, which is the greatest common divisor. This result is at least as slow as the input frequencies or even slower.

- An abstract event-based activation condition is a set containing all input streams, which need to be contained in an incoming event to evaluate the stream. Therefore, the set of the meet operator consists of all elements which are in one of the arguments, resulting in the union, with the bottom element *Stream*.

**Remark 3.1.6** (Optional Types). Some expressions, i.e. offset lookups or sample & hold, return an optional value, because the monitor cannot guarantee the existence of a value. To see the need for optional return types in the lattice, we consider the following specification, assuming that optional values are treated as non-optional ones:

```

input a : Int8

output b : Int8 := a + b.offset(by:-1)

```

This specification adds up all values from the input stream a with the output stream b. Without using optional value types, it is intuitively clear, even without knowing the complete semantics of RTLola, that the type checker would allow the expression a + b.offset(by:-1), because a and b have the same value type Int(8). However, in the first iteration the previous value of b is not defined resulting in an error. Therefore, to represent optional values in the type lattice, we introduce an additional abstract value type  $Opt(\widetilde{VT})$ , lifting the value types to optional types.

**Remark 3.1.7** (Meet-semi Lattice Proof). Schwenger [25] proved that the lattice defined in Definition 11 is a meet-semilattice, by proving associativity, commutativity, and idempotency for the meet operator  $\sqcap$ . The proof first shows the properties for each meet operator  $\sqcap_{VT}$ ,  $\sqcap_{ET}$ , and  $\sqcap_{PT}$  and then follows that the combination also results in a meet operator.

#### Type Checking

The overall goal of the type checker is performing an analysis which finds expressions that are incompatible to each other. This includes expressions with different activation conditions, e.g. a synchronous lookup to an event-based stream from a periodic-output stream. But it also includes value type errors, e.g. multiplying a boolean stream with a number. Before we perform the type checking analysis, we define a relation  $\models$  for type validity. We denote that an abstract type  $(\widetilde{\sigma}, \widetilde{\tau})$  is a model for an expression e, with a binary relation  $\models$  by:  $\widetilde{\sigma}, \widetilde{\tau} \models e$ . Based on this relation, the type checker uses inference rules, which are defined for each stream and expression individually. To apply the inference rules for expressions, we first need to lift the concrete stream value types to abstract ones. Therefore, the inference for streams uses the following generalization function:

**Def.** Generalization Function

**Definition 12** (Generalization Function [25])

The *generalization function lift* :  $VT \rightarrow \widetilde{VT}$  for a concrete value type  $\tau$  is defined as:

$$lift(\tau) := \begin{cases} \{Bool\} & \text{if} \quad \tau = Bool \\ \{X(z) \mid \{8, 16, 32, 64\} \ni z \ge y\} & \text{if} \quad \tau = X(y), y \in \{8, 16, 32, 64\}, \\ X \in \{Int, UInt, Float\} \end{cases}$$

In each inference rule we check for each stream and expression if the abstract value type and activation satisfies the expression or stream. If the expression or stream is a non-leaf node in the AST, we additionally check for each child if the abstract type satisfies the subexpression.

To get a intuition for the inference rules, consider the inference rule for default expressions:

$$\frac{\widetilde{\sigma_1},\widetilde{\tau_1}\models e_1\quad \widetilde{\sigma_2},\widetilde{\tau_2}\models e_2\quad \widetilde{\sigma_1}=Opt\langle\widetilde{\sigma_1}'\rangle\quad \widetilde{\sigma}\sqsubseteq\widetilde{\sigma_1}'\cap\widetilde{\sigma_2}\quad \widetilde{\tau}\sqsubseteq\widetilde{\tau_1}\cap\widetilde{\tau_2}}{\widetilde{\sigma},\widetilde{\tau}\models Default(e_1,e_2)}$$

A default expression returns a default value in case of a lookup fail, resulting in two subexpressions. For this, the inference rule checks the compatibility of the subexpressions: First, it finds the abstract value types and activation conditions for each subexpression. For these abstract types, the rule defines the following constraints: The first constraint checks if the abstract value type of the first subexpression is an optional value. Intuitively, to represent a lookup fail RTLola uses optional types. In case that the first expression does not return an optional type, i.e. no lookup fail is possible, the default value would never be taken and therefore the default expression is not needed. This behavior needs to be detected by the type checker. The second constraint then checks if the value type of both subexpressions are comparable, and refines the value type of the default expression. Because the default expression resolves the lookups fails, this check does not use the optional abstract type of the first sub expression, but the abstract value type stored in the optional one. The third constraint then compares and refines the activation condition.

The most restricted inference rule is for sliding window lookups, defined as:

$$\frac{\delta \in \mathbb{N} \quad \gamma \colon T_a^* \to T_r \quad \tau \sqsubseteq lift(T_r) \quad \widetilde{\sigma}', \widetilde{\tau}' \models s_i^- \quad \widetilde{\tau}' \sqsubseteq lift(T_a)}{\widetilde{\pi}, \widetilde{\tau} \models Window(s_i^-, \delta, \gamma)}$$

In comparison to all other rules, sliding window lookups enforce abstract periodic types in the relation. Before, we give an intuition, we recap the behavior of sliding windows. A sliding window aggregates over all values of a stream  $s_i^-$  during a specified duration. For this reason, when reaching a time point, where to evaluate a stream expression  $s_j^{\uparrow}$ , with a sliding window lookup, the window needs to decide which values of  $s_i^-$  are part of the current window. If we restrict the activation condition of sliding windows

to a periodic type, the time points when evaluating a stream are statically known. As a consequence, the windows of the sliding window lookup are also statically known, which simplifies the decision which stream values are part of the window, even if they arrive in non-fixed time steps. Section 3.1.4 discusses the evaluation of sliding windows more detailed. Another constraint resulting from the sliding windows is the duration. Similar to the restrictions for the frequency, Schwenger [25] restricts the duration to a natural number simplifying the correctness proofs. However, in general RTLola is capable to describe constraints without these restrictions. Another constraint from the inference rule for sliding window lookups results from the aggregation function. To evaluate the window, the function uses the stream values from  $s_i^-$ . Therefore, the type  $T_i^{\uparrow}$  needs to be compatible with the input type of the function. The same constraint holds for the return type, which needs to be compatible with the window lookup.

→ Sec. 3.1, P. 24

**Remark 3.1.8.** A list of all inference rules is presented in Appendix A.1. We do not discuss all rules separately. If you are interested in the details, a complete description of all inference rules is presented by Schwenger [25]. Nevertheless, we present in this thesis the general concept, with the following examples.

→ App. A.1, P. 115

With the inference rules and the binary relation, we define the *type validity* of a specification.

#### **Definition 13** (Type Validity [25])

A specification has *valid types* if and only if for every stream and trigger there is a non-contradictory value type and activation condition.

**Def.** Type Validity

$$\forall s_i^- \exists \widetilde{\sigma}, \widetilde{\tau} : \widetilde{\sigma}, \widetilde{\tau} \models s_i^- \land \widetilde{\sigma} \neq \bot \land \widetilde{\tau} \neq \bot$$

With type validity, we defined the last constraint for a valid specification, resulting in the definition:

**Definition 14** (Specification Validity [25])

A RTLola specification is *valid* iff it satisfies the following three criteria on its syntax, dependency graph, and types:

Specification

• Syntactic validity according to Definition 1

→ Sec. 3.1, P. 10

• Well-formedness according to Definition 4

→ Sec. 3.1, P. 13

• Type validity according to Definition 13

→ Sec. 3.1, P. 23

**Remark 3.1.9** (Formal Semantics). Schwenger [25] defined a formal semantics assuming infinite memory. Therefore, he first introduces the concept of relevant timestamps, which compromises all possible timestamps to the timestamps, where at least one activation condition of all streams is satisfied. Then, he defines the evaluation process with an infinite memory

model, and afterward, the expression evaluation. The focus of this section is getting an intuition for the specification language, which provides a tradeoff between expressiveness and formal guarantees. If you need more details about the formal semantics of RTLOLA, we refer to [25, 12].

One essential guarantee for the hardware realization is a finite memory model. Therefore, if we analyze the dependency graph and restrict the aggregation function to get an upper bound for each stream entity and sliding window, we can compress the infinite model to a finite one. This analysis and the restriction on the aggregation functions are intuitively outlined in the following paragraph.

#### 3.1.4. Finite Memory Monitoring

In the previous section, we defined the conditions for a valid specification. Before we describe a realization for such specifications, we first define memory upper bounds on the stream entities to realize the monitor with finite and statically known memory. This includes the evaluation of the activation type as well as for the expression evaluation. Additionally, we have to restrict the aggregation function for a finite memory realization.

#### Handling Time

→ Sec. 3.1, P. 17

Section 3.1.3 introduces two types of activation conditions, event-based and periodic. The activation condition of event-based streams is bounded to the incoming event, e.g. an output stream b with the activation condition  $\{a,b\}$  is evaluated with each event that updates the input streams a and b. Because the monitor has no control about the timing of the incoming events, the timing of event-based streams cannot be determined statically. As a complement, period streams are annotated with a frequency which bounds the activation condition to fixed-time points, e.g. an output stream b with activation condition 2Hz is evaluated every 500ms. Due to the fixed time stamps, we can define statically a global *schedule* for all periodic streams. The entries of the schedule then contain a time stamp and a non-empty set of period output stream, with the following notation:

Schedule

Deadline

Hyper-Period

- We call a time stamp in the schedule a *deadline*.

- We say a deadline is due if the monitor reaches a timestamp which is part of the schedule.

To find a finite representation for the schedule, we use the hyper-period. The *hyper-period*  $\Pi$  of a specification is the least common multiple of all frequencies in the specification:

$$\Pi = \operatorname{lcm}(\{p^{-1} \mid p \in P^{spec}\})$$

Intuitively, the hyper-period describes the duration until the schedule repeats its entries. With this concept, we define a finite schedule dl, which the monitor repeats every hyperperiod. Beside the deadline array we additionally define an offset array off, which stores the time difference between two consecutive deadlines.

24

#### **Example 3.1.7** (Schedule). Consider the following specification:

```

input a : Int8

output b : Int8 @4Hz := a.hold().defaults(to: 0) + 2

output c : Int8 @2Hz := b + 3

output d : Int8 @5Hz := a.aggregate(over: 2s, using: ∑)

```

In this example the output stream b is evaluated every 250ms, the output stream c every 500ms, and the output stream d every 200ms. This results in the hyper-period  $\Pi = 1$ s, in the schedule dl, and in the offset array off:

| $dl(0) \coloneqq (200 \text{ms}, \{d\})$   | off(0) := 50ms  |

|--------------------------------------------|-----------------|

| $dl(1) \coloneqq (250 \text{ms}, \{b\})$   | off(1) := 150ms |

| $dl(2) \coloneqq (400 \text{ms}, \{d\})$   | off(2) := 100ms |

| $dl(3) \coloneqq (500\text{ms}, \{b, c\})$ | off(3) := 100ms |

| $dl(4) \coloneqq (600 \text{ms}, \{d\})$   | off(4) := 150ms |

| $dl(5) \coloneqq (750 \text{ms}, \{c\})$   | off(5) := 50ms  |

| $dl(6) \coloneqq (800\text{ms}, \{d\})$    | off(6) := 200ms |

| $dl(7) := (1000 ms, \{b, c, d\})$          | off(7) := 200ms |

|                                            |                 |

#### Finite Memory Handling

Section 3.1.1 presents the types of stream expressions, including different lookups and function calls. The monitor accesses stream values to evaluate the expressions, which needs to be stored. A naive implementation would store every computed or received value to guarantee that the expression evaluation has access to the values. This approach is sane assuming infinite memory. However, in practice this assumption does not hold, and the size of the input data is necessary to guarantee the absence of buffer overflows. Otherwise the monitor loses its guarantees which is critical if monitoring is used as the safety component of a system. Again the assumption of knowing the size of the input data cannot be applied in practice, such that we need another approach, which identifies the memory consumption statically based on the specification. To realize an approach with finite memory, we first assume specifications without sliding window lookups.

The syntax statically encodes which values will be addressed by the stream expression. Thus, we can analyze for each stream the *storage requirement* from the specification, which contains the number of stream values which will be accessed. For illustration, consider the following example which contains all possible lookups:

**Def.** Storage Requirement

→ Sec. 3.1, P. 7

Δ

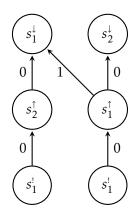

Figure 3.2.: Dependency graph for the specification in Example 3.1.9.

#### **Example 3.1.8** (Storage Requirement). Consider the following specification:

```

input a : Int8

input b : Int8

output c : Bool := a + b.offset(by:-1).defaults(to: 0) < 3

output d : Bool @1Hz := a.hold().defaults(to:1) < 3

trigger c "c is smaller than 6"

trigger d "a is smaller than 3"</pre>

```

In this specification, a is accessed with a synchronous lookup and a sample & hold lookup. In both cases, the expression targets the current value of the stream and the monitor does not need to store any previous values. The input stream b is accessed with an offset lookup of -1. Therefore, the current stream value and the previous value need to be stored. The output streams c and d are synchronously accessed by the triggers, such that the storage requirement for both streams is 1. Triggers cannot be addresses by stream expressions resulting in no storage requirement.

The information about the storage requirement per stream is encoded in the dependency graph, resulting in the following definition:

#### **Definition 15** (Storage Requirement [25])

The storage requirement  $\kappa(s)$  of stream s is the maximum offset of stream lookups with target s based on the dependency graph DG = (V, E).

$$\kappa(s_i^{\scriptscriptstyle{-}}) \coloneqq \max\{w \mid \exists s_i^{\scriptscriptstyle{\uparrow}} \colon (s_i^{\scriptscriptstyle{\uparrow}}, w, s_i^{\scriptscriptstyle{-}}) \in E \land w \in \mathbb{N}\} + 1$$

**Example 3.1.9.** Figure 3.2 represents the dependency graph of the specification in Example 3.1.8. It represents that the storage requirement corresponds to the maximal offset of the incoming edges in the dependency graph:

$$\kappa(s_1^{\downarrow}) = 1 \qquad \qquad \kappa(s_2^{\downarrow}) = 2 \qquad \qquad \kappa(s_1^{\uparrow}) = 1 \qquad \qquad \kappa(s_2^{\uparrow}) = 1 \qquad \qquad \Delta$$

In the next step, we now include sliding window accesses again, starting with the following specification:

```

input a : Int8

output b : Int8 := a.aggregate(over: 1s, using: sum)

```

The sliding window in the output stream b adds up all input values during the last second. Once again, a naive implementation would store all incoming events  $a_1, \ldots, a_n$  and adds up all values, i.e.  $\sum_{1 \le i \le n} a_i$ . This approach is sane and the sliding window would return the correct value. However, this approach infers two problems. First, with every new event the function adds up all values, e.g. with a new event  $a_{n+1}$  the windows computes  $\sum_{1 \le i \le n+1} a_i$ . However, most of the values are already computed with the previous event so a better approach would be re-use the old result  $\sum_{1 \le i \le n} a_i$ , resulting in  $(\sum_{1 \le i \le n} a_i) + a_{n+1}$ . Another problem with storing all incoming values is the memory consumption. The monitor has no restrictions on how many events can be received during the window. Therefore, if we store all events we would need infinite memory. To solve this issue, we restrict the aggregation functions to *list homomorphisms*. With this limitation, we re-use computations with a constant runtime and constant memory.

#### **Definition 16** (Homomorphism [26])

A *list homomorphism*  $\gamma: A^* \to B$  can be split into four components:

**Def.** List Homomorphism

- an unary function  $map_{\gamma} \colon A \to T$  lifting a single value into an intermediate representation

- a unary finalization function  $fin_{\gamma} \colon T \to B$  lowering an intermediate value to a result

- an associative binary reduction function  $\circledast_{\gamma} \colon T \times T \to T$ , i.e.,  $(a \circledast_{\gamma} b) \circledast_{\gamma} c = a \circledast_{\gamma} (b \circledast_{\gamma} c)$

- a neutral element  $\varepsilon_{\gamma} \in T$  w.r.t.  $\circledast_{\gamma}$ , i.e.  $a \circledast_{\gamma} \varepsilon_{\gamma} = \varepsilon_{\gamma} \circledast_{\gamma} a = a$  for any  $a \in T$ .

**Example 3.1.10** (Add List Homomorphism). The list homomorphism for the addition iteratively adds up all incoming events and is defined as:

- $map_{sum}: A \rightarrow A \text{ with } map_{sum}(x) = x$

- $fin_{sum}: A \rightarrow A \text{ with } fin_{sum}(x) = x$

- $\circledast_{sum}: A^2 \to A \text{ with } x_1 \circledast_{sum} x_2 = x_1 + x_2$

- $\varepsilon_{sum} = 0$

Δ

With the following theorem, we can iteratively pre-aggregate the intermediate values, store them, and can re-use the values for following computations. For example, to compute the n+1-th value  $v_{n+1} = \operatorname{fin}(\operatorname{map}(a_1) \circledast_{\gamma} \dots \circledast_{\gamma} \operatorname{map}(a_{n+1}))$ , we can use the preaggregated values  $i_{1\dots n} = \operatorname{map}(a_1) \circledast_{\gamma} \dots \circledast_{\gamma} \operatorname{map}(a_n)$  as input for the finalization function, resulting in  $v_{n+1} = \operatorname{fin}(i_{1\dots n} \circledast_{\gamma} \operatorname{map}(a_{n+1}))$ .

**Theorem 3** (Meertens [26]). The aggregation of  $v_1, ..., v_n$  using a list homomorphism  $\gamma$  can be broken into arbitrary sub-aggregations. Let  $(I_i)_{i \leq k} = ((x_{i,j})_{j \leq |I_i|})_{i \leq k}$  for some  $k \in \mathbb{N}$  be an ordered partition of the interval [1, ..., n].

$$\gamma(v_1,\ldots,v_n) = fin_{\gamma}((map_{\gamma}(x_{1,1}) \circledast_{\gamma} \ldots \circledast_{\gamma} x_{1,|I_1|}) \circledast_{\gamma} \ldots \circledast_{\gamma} (map_{\gamma}(x_{k,1}) \circledast_{\gamma} \ldots \circledast_{\gamma} map_{\gamma}(x_{k,|I_1|})))$$

Because we can re-use the results in the intermediate representation, the sliding window can be pre-computed. For this reason, the evaluation of sliding window expression is performed with constant memory in the size of the intermediate representation. In the previous example, the intermediate representation is a single value. However, this is not true in general shown with the next example:

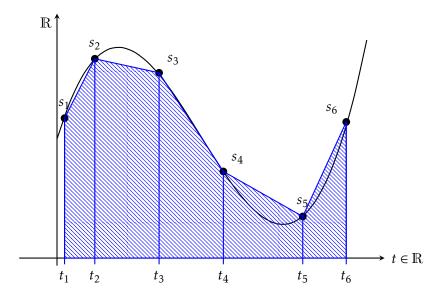

**Example 3.1.11** (Integration List Homomorphism). For the integration function, the input values are tuples  $(v,t) \in V \times T$ , where v is the current value and t is the corresponding time stamp. To compute the integral, we use the trapezoid construction, a numerical approach represented in Figure 3.3. This approach constructs from samples of the function trapezoids and calculates the area of the trapezoids. With a decreasing difference between the sample, the trapezoids gets more accurate and the approximated value corresponds more to the concrete integral. This results in the following list homomorphism:

- $map_{\int}: (A,T) \to Optional(A,T,A,T,A)$  with  $map_{\int}((x,t)) = (x,t,x,t,0)$

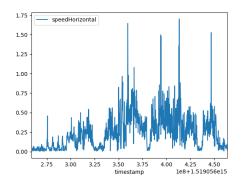

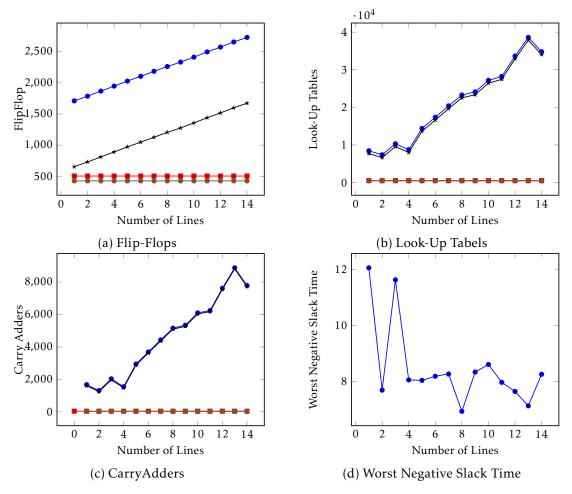

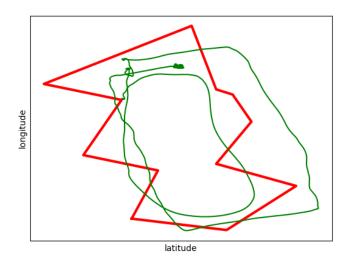

- $fin_{\int}: Optional(A, T, A, T, A) \rightarrow Optional(A)$  with  $fin_{\int}(\bot) = \bot$  and  $fin_{\int}((x^L, t^L, x^R, t^R, v)) = v$