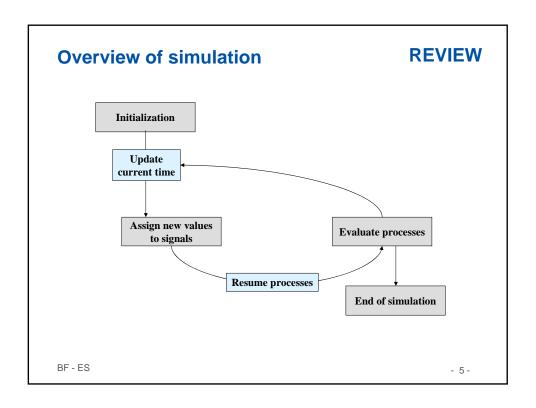

#### **Initialization**

#### **REVIEW**

- At the beginning of initialization, the current time,  $t_{\rm curr}$  is assumed to be 0 ns.

- An initial value is assigned to each signal.

- Taken from declaration, if specified there, e.g.,

- signal s : std\_ulogic := `0`;

- Otherwise: First value in enumeration for enumeration based data types, e.g.

- **signal** s : std\_ulogic type std\_ulogic is (`U`, `X`, `0`, `1`, `Z`, `W`, `L`, `H`, `-`); ⇒ initial value is `U`

- This value is assumed to have been the value of the signal for an infinite length of time prior to the start of the simulation.

- Initialization phase executes each process exactly once (until it suspends).

- During execution of processes: Signal assignments are collected in transaction list (not executed immediately!) - more details later.

- If process stops at "wait for"-statement, then update process activation list more details later.

- After initialization the time of the next simulation cycle (which in this case is the first simulation cycle), t<sub>next</sub> is calculated:

Time t<sub>next</sub> of the next simulation cycle = earliest of 1. time high (end of simulation time).

2. Earliest time in transaction list (if not empty)

- 3. Earliest time in process activation list (if not empty). BF - ES

- 6-

# Signal assignment phase – first part of step

## **REVIEW**

- Each simulation cycle starts with setting the current time to the next time at which changes must be considered:

- $t_{curr} = t_{next}$

- This time t<sub>next</sub> was either computed during the initialization or during the last execution of the simulation cycle. Simulation terminates when the current time would exceed its maximum, time'high.

- For all (s, v, t<sub>curr</sub>) in transaction list:

- Remove (s, v, t<sub>curr</sub>) from transaction list.

- s is set to v.

- For all processes p<sub>i</sub> which wait on signal s:

- Insert (p<sub>i</sub>, t<sub>curr</sub>) in process activation list.

- Similarly, if condition of "wait until"-expression changes value.

BF - ES - 7 -

# Process execution phase – second part of step (1)

## **REVIEW**

- Resume all processes p<sub>i</sub> with entries (p<sub>i</sub>, t<sub>curr</sub>) in process activation list.

- Execute all activated processes "in parallel" (in fact: in arbitrary order).

- Signal assignments

- are collected in transaction list (not executed immediately!).

- Examples:

- s <= a and b;</li>

- Let v be the conjunction of current value of a and current value of b.

- Insert (s, v, t<sub>curr</sub>) in transaction list.

- s <= '1' after 10 ns;</li>

- Insert (s, '1',  $t_{curr}$  + 10 ns) into transaction list.

- Processes are executed until wait statement is encountered.

- If process p<sub>i</sub> stops at "wait for"-statement, then update process activation list:

- Example:

- p<sub>i</sub> stops at "wait for 20 ns;"

- Insert (p<sub>i</sub>, t<sub>curr</sub> + 20 ns) into process activation list

BF - ES - 8 -

# Process execution phase – second part of step (2)

#### **REVIEW**

If some process reaches last statement and

- does not have a sensitivity list and

- last statement is not a wait statement,

then it continues with first statement and runs until wait statement is reached.

- When all processes have stopped, the time of the next simulation cycle  $t_{next}$  is calculated:

- Time  $t_{next}$  of the next simulation cycle = earliest of

- 1.time high (end of simulation time).

- 2. Earliest time in transaction list (if not empty)

- 3. Earliest time in process activation list (if not empty).

- Stop if t<sub>next</sub> = time'high and transaction list and process activation list are empty.

BF-ES - 9-

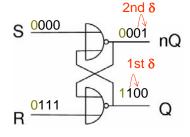

# Delta delay - Simulation of an RS-Flipflop

## **REVIEW**

|    | 0ns | 0ns+ $\delta$ | 0ns+2δ |

|----|-----|---------------|--------|

|    | 1   | 1             | 1      |

| s  | 0   | 0             | 0      |

| Q  |     | 0             | 0      |

| nζ | 0 0 | 0             | 1      |

BF - ES

```

entitiy RS_Flipflop is

port (R, S : in std_logic;

Q, nQ : inout std_logic);

end RS_FlipFlop;

```

architecture one of RS\_Flipflop is begin process (R,S,Q,nQ) begin Q := R nor nQ; nQ := S nor Q; end process;

$\delta$  cycles reflect the fact that no real gate comes with zero delay.

end one;

- 10 -

## "Write-write-conflicts"

## **REVIEW**

# signal s : bit; ... p : process begin ... s <= '0'; ... s <= '1'; wait for 5 ns; end process p;</pre>

#### Case 1:

Write-write-conflicts are restricted to the same process (i.e. they occur inside the same process)

- Then the second signal assignment overwrites the first one.

- This is the only case of "non-concurrency" of signal assignments

- Note that writing to different signals occurs concurrently, however!

BF - ES

## "Write-write-conflicts"

#### **REVIEW**

- 11 -

#### Case 2:

Write-write-conflicts between different processes (explicit or implicit processes)

- If there is no "resolution function" for the data type *dt*, then writing the same signal by different processes in the same step is **forbidden**.

- If there is a resolution function, then the resolution function computes the value of s at time t<sub>curr</sub>:

- Value for s in the current step is computed for each process separately,

- "resolution function" for different values is used to compute final result.

- In the following:

Data type std\_ulogic with resolution function ⇒ data type std\_logic

BF - ES - 12 -

# Multi-valued logic and standard IEEE 1164

#### **REVIEW**

- How many logic values for modeling?

- Two ('0' and '1') or more?

- If real circuits have to be described, some abstraction of the resistance (inversely-related to the strength) is required.

- ⇒ We introduce the distinction between:

- the logic level (as an abstraction of the voltage) and

- the strength (as an abstraction of the current drive capability) of a signal.

- Both logic level and strength are encoded in logic values.

BF - ES - 13 -

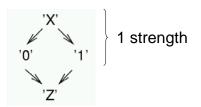

## 1 signal strength

#### **REVIEW**

- Logic values '0' and '1'.

- Both of the same strength.

- Encoding false and true, respectively.

- No meaningful "resolution function" possible, if `0` and `1` are written to the same signal at the same time.

BF - ES - 14 -

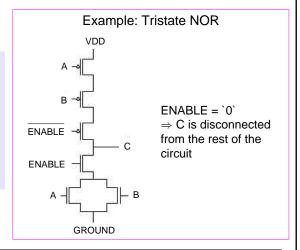

## 2 signal strengths (1)

## **REVIEW**

- Many subcircuits can be effectively disconnected from the rest of the circuit (they provide "high impedance" values to the rest of the circuit).

- Example: subcircuits with tri-state outputs.

We introduce signal value 'Z', meaning "high impedance "

BF - ES

- 15 -

## 2 signal strengths (2)

## **REVIEW**

- We introduce an operation #, which generates the effective signal value whenever two signals are connected by a wire ("resolution").

- #('0','Z')='0'; #('1','Z')='1'; '0' and '1' are "stronger" than 'Z'

According to the partial order in the diagram, # returns the larger of the two arguments.

In order to define #('0','1'), we introduce 'X', denoting an undefined signal level. 'X' has the same strength as '0' and '1'.

BF - ES

- 16 -

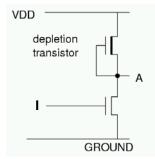

## 3 signal strengths

## **REVIEW**

Current set of values insufficient for describing real circuits:

Example: nMOS-Inverter

Depletion transistor (resistor) contributes a weak value to be considered in the #-operation for signal A

Introduction of 'H', denoting a weak signal of the same level as '1'.

$$\#('H', '0')='0'; \ \#('H, 'Z')='H'$$

BF - ES

17

## 3 signal strengths

## **REVIEW**

- ■There may also be weak signals of the same level as '0'

- Introduction of 'L', denoting a weak signal of the same level as '0':

$$\#('L', 'O')='O'; \#('L, 'Z') = 'L';$$

■ Introduction of 'W', denoting a weak signal of the same level as 'X':

$$\#('L', 'H')='W'; \#('L, 'W')='W';$$

\*# reflected by the partial order shown.

strongest

'X'

'0'

'1'

weakest

'X'

'Y'

W'

'H'

weakest

BF - ES

- 18 -

IEEE 1164 REVIEW

- VHDL allows user-defined value sets.

- ⇒ Each model could use different value sets (unpractical)

- ⇒ Definition of standard value set according to standard IEEE 1164:

- First seven values as discussed previously.

- 'U': un-initialized signal; used by simulator to initialize all not explicitly initialized signals: type std\_ulogic is (`U`, `X`, `0`, `1`, `Z`, `W`, `L`, `H`, `-`);

- '-': is used to specify don't cares:

- Example: if a /= '1' or b/='1' then f <= a exor b; else f <= '-';</p>

- '-' may be replaced by arbitrary value by synthesis tools.

BF - ES - 19 -

## **Outputs tied together**

In hardware, connected outputs can be used:

unresolved resolved signal bus signals outputs

Modeling in VHDL: resolution functions type std\_ulogic is ('U', 'X','0', '1', 'Z', 'W', 'L', 'H', '-'); subtype std\_logic is resolved std\_ulogic;

BF - ES - 20 -

## **Resolution function for IEEE 1164**

```

type std_ulogic_vector is array(natural range<>)of std_ulogic;

function resolved (s:std_ulogic_vector) return std_logic is

variable result: std_ulogic:='Z'; --weakest value is default

begin

if (s'length=1) then return s(s'low) --no resolution

else for i in s'range loop

result:=resolution_table(result,s(i))

end loop

end if:

return result;

end resolved;

BF - ES

```

- 21 -

## **Resolution function for IEEE 1164**

```

constant resolution_table : stdlogic_table := (

--U

Χ

0

1

Z W

H -

L

'U', 'U', 'U'),

('U', 'U', 'U', 'U', 'U', 'U',

--| U |

('U', 'X', 'X', 'X', 'X', 'X',

'X', 'X', 'X'),

--| X |

('U', 'X', '0', 'X', '0', '0',

--|0|

'0', '0', 'X'),

('U', 'X',

'X', '1', '1', '1',

'1', '1', 'X'),

--|1|

('U', 'X',

'0', '1', 'Z', 'W',

'L', 'H', 'X'),

--| Z |

('U', 'X', '0', '1', 'W', 'W',

'W', 'H', 'X'), --| W |

('U', 'X',

'0',

'1', 'L', 'W',

'L', 'W', 'X'),

--| L |

('U', 'X', '0', '1', 'H', 'W',

'W', 'H', 'X'), --| H |

('U', 'X', 'X', 'X', 'X', 'X',

'X', 'X', 'X')

);

BF - ES

- 22 -

```

## Inertial and transport delay model

- Signal assignment:

- Example:

- Inpsig <= '0', '1'after 5 ns, '0' after 10 ns, '1' after 20 ns;</li>

BF-ES - 23-

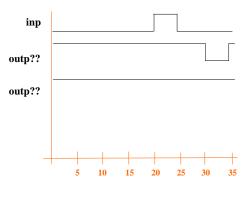

## Inertial and transport delay model

Example for signal assignment: outp <= not inp after 10 ns;</p>

BF - ES - 24 -

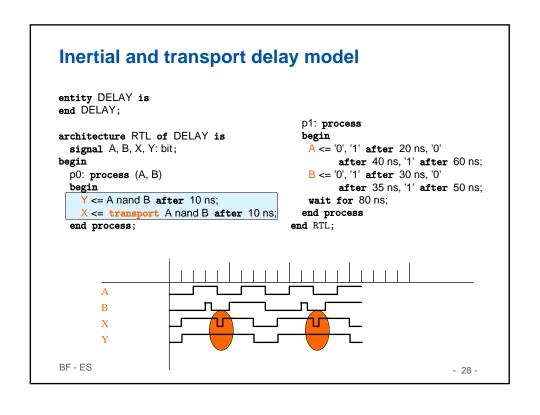

## Inertial and transport delay model

Two delay models in VHDL:

- Inertial delay ("träge Verzögerung")

- Transport delay ("nichtträge Verzögerung")

Inertial delay model is motivated by the fact that physical gates absorb short pulses (spikes) at their inputs (due to internal capacities)

BF - ES - 25 -

## Inertial delay model Input Output Inverter ... is the default model! INERTIAL is the default Output <= NOT input AFTER 10 ns; Allows to specify the delay of a gate or operation Output Absorbs pulses at the inputs which are shorter Input than the delay specified for the gate / operation BF - ES - 26 -

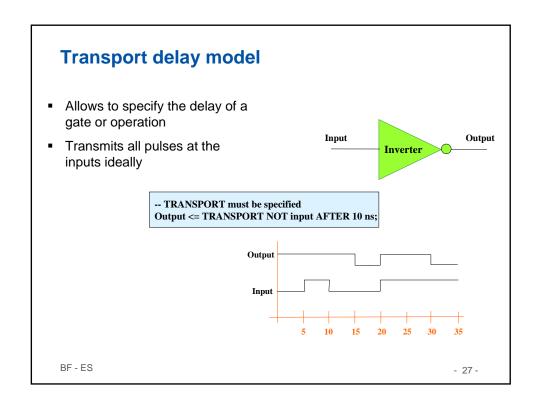

## Semantics of transport delay model

- Restriction (at first):

- Do not consider resolution etc., i.e., assignments to a fixed signal only made in one process

- Signal assignments change transaction list.

- Before transaction (s, t₁, v₁) is inserted into transaction list, all transactions in the transaction list (s, t₂, v₂) with t₂ ≥ t₁ are removed from transaction list.

BF - ES - 29 -

#### **Example for transport delay model** inv : process(inp) begin if inp='1' then outp <= transport '0' after 20 ns;</pre> inp outp elsif inp='0' then Inverter outp <= transport '1' after 12.5 ns end if; end process inv; Transaction list: At 5ns: outp (outp, 25ns, `0`) At 10 ns: (outp, 22.5ns, `1`), (outp, 25ns, `0`) inp Remove (outp, 25ns, `0`)! (outp, 22.5ns, `1`) 15 20 25 10 30 BF - ES - 30 -

## Semantics of inertial delay model

- Semantics for more general version of inertial delay statement:

- Inertial delay absorbs pulses at the inputs which are shorter than the delay specified for the gate / operation.

- Key word reject permits absorbing only pulses which are shorter than specified delay:

- Example:

- outp <= reject 3 ns inertial not inp after 10 ns;

- Only pulses smaller than 3 ns are absorbed.

- outp <= reject 10 ns inertial not inp after 10 ns;</li>

and

outp <= not inp after 10 ns;</li>

are equivalent.

BF - ES - 31 -

## Semantics of inertial delay model

- Same restriction as for transport model (at first):

- Do not consider resolution etc., i.e., assignments to a fixed signal only made in one process

- Rule 1 as for transport delay model: Before transaction (s,  $t_1$ ,  $v_1$ ) is inserted into transaction list, all transactions in the transaction list (s,  $t_2$ ,  $v_2$ ) with  $t_2 \ge t_1$  are removed from transaction list.

- Rule 2 removes also some transactions with times < t<sub>1</sub>:

- Suppose the time limit for reject is rt.

- Transactions for signal s with time stamp in the intervall (t<sub>1</sub> rt, t<sub>1</sub>) are removed.

- Exception:

If there is in (t<sub>1</sub> rt, t<sub>1</sub>) a subsequence of transactions for s immediately before (s, t<sub>1</sub>, v<sub>1</sub>) which also assign value v<sub>1</sub> to s, then these transactions are preserved.

BF - ES - 32 -

## **Example**

```

process

begin

o1 <= transport '0', '0' after 5ns, '1' after 15 ns, '0' after 20ns,

'1' after 25 ns, '1' after 30ns, '1' after 45 ns,

'0' after 50 ns;

-- same signal assignment for o2

o2 <= transport '0', '0' after 5ns, '1' after 15 ns, '0' after 20ns,

'1' after 25 ns, '1' after 30ns, '1' after 45 ns,

'0' after 50 ns;

wait for 15 ns;

o2 <= reject 22 ns inertial '1' after 25 ns;

wait;

end process;

Transaction list until "wait for 15 ns":

```

(o1, 0ns, '0'), (o1, 5ns, '0'), (o1, 15ns, '1'), (o1, 20ns, '0'), (o1, 25ns, '1'), (o1, 30ns, '1'), (o1, 45ns, '1'), (o1, 50ns, '0'), (o2, 0ns, '0'), (o2, 5ns, '0'), (o2, 15ns, '1'), (o2, 20ns, '0'), (o2, 25ns, '1'), (o2, 30ns, '1'), (o2, 45ns, '1'), (o2, 50ns, '0') Transaction list when process is reactivated at time 15ns:

(o1, 20ns, `0'), (o1, 25ns, `1'), (o1, 30ns, `1'), (o1, 45ns, `1'), (o1, 50ns, `0'), (o2, 20ns, `0'), (o2, 25ns, `1'), (o2, 30ns, `1'), (o2, 45ns, `1'), (o2, 50ns, `0')

BF - ES

- 33 -

## **Example**

```

process

begin

o1 <= transport '0', '0' after 5ns, '1' after 15 ns, '0' after 20ns,

'1' after 25 ns, '1' after 30ns, '1' after 45 ns,

'0' after 50 ns;

-- same signal assignment for o2

o2 <= transport '0', '0' after 5ns, '1' after 15 ns, '0' after 20ns,

'1' after 25 ns, '1' after 30ns, '1' after 45 ns,

'0' after 50 ns;

wait for 15 ns;

o2 <= reject 22 ns inertial '1' after 25 ns;

end process;

```

- At time 15ns:

- insert transaction (o2, 40ns, `1`).

- $\blacksquare \quad \text{Remove transactions with time stamp} \geq 40 \text{ns}.$

- Results in preliminary transaction list: (01, 20ns, `0'), (01, 25ns, `1'), (01, 30ns, `1'), (01, 45ns, `1'), (01, 50ns, `0'), (02, 20ns, `0'), (02, 25ns, `1'), (02, 30ns, `1'), (02, 40ns, `1')

BF - ES - 34 -

```

Example

process

begin

o1 <= transport '0', '0' after 5ns, '1' after 15 ns, '0' after 20ns,

'1' after 25 ns, '1' after 30ns, '1' after 45 ns,

'0' after 50 ns;

-- same signal assignment for o2

o2 <= transport '0', '0' after 5ns, '1' after 15 ns, '0' after 20ns,

'1' after 25 ns, '1' after 30ns, '1' after 45 ns,

'0' after 50 ns;

wait for 15 ns;

o2 <= reject 22 ns inertial '1' after 25 ns;

wait;

end process;

Rule 2:

Transactions for signal o2 with

Results in preliminary transaction list: (o1, 20ns, `0'), (o1, 25ns, `1'), (o1, 30ns, `1'), (o1, 45ns, `1'), (o1, 50ns, `0'), (o2, 20ns, `0'), (o2, 25ns, `1'), (o2, 30ns, `1'), (o2, 40ns, `1')

time stamp in the intervall (40ns -

22ns, 40ns) = (18ns, 40ns) are

removed.

Rule 2:

Exception:

(o2, 25ns, `1`), (o2, 30ns, `1`) are preserved,

(o2, 20ns, `0`), is removed.

If there is in (18ns, 40ns) a

subsequence of transactions for

Resulting transaction list: (o1, 20ns, '0'), (o1, 25ns, '1'), (o1, 30ns, '1'), (o1, 45ns, `1'), (o1, 50ns, `0'), (o2, 25ns, '1'), (o2, 30ns, '1'), (o2, 40ns, '1')

o2 immediately before

(o2, 40ns, `1`) which also assign

value `1` to o2, then these

transactions are preserved.

```

#### **Example** process begin o1 <= transport '0', '0' after 5ns, '1' after 15 ns, '0' after 20ns, '1' after 25 ns, '1' after 30ns, '1' after 45 ns, '0' **after** 50 ns; -- same signal assignment for o2 o2 <= transport '0', '0' after 5ns, '1' after 15 ns, '0' after 20ns, '1' after 25 ns, '1' after 30ns, '1' after 45 ns, '0' **after** 50 ns; wait for 15 ns; o2 <= reject 22 ns inertial '1' after 25 ns; wait; end process; Resulting wave form: o2**o1** BF - ES - 36 -35 40 45 10 15 20 25 30

## Inertial and transport delay model

For signal assignments of form Inpsig <= '0' after 5 ns, '1' after 10 ns, '0' after 15 ns, '1' after 20 ns;

only the first assignment follows the inertial delay model.

- If there are assignments to a signal s in several processes p<sub>1</sub>, ..., p<sub>n</sub>:

- Insert entries of form (s<sup>Pi</sup>, t, v) into transaction list ("for each signal driver separate entries")

- Apply rules for inertial/transport delay model as defined above (separately) to signals s<sup>Pi</sup>.

- If there are several entries (s<sup>Pi</sup>, t<sub>curr</sub>, v<sub>i</sub>) in current assignment phase:

- Apply resolution function to compute resulting value for assignment to s.

BF - ES - 37 -

## Some additional language elements

- VHDL supports usual elements of imperative programming languages, e.g.,

- Various data types

- scalar data types like integers, reals, enumeration types, physical types,

- arrays,

- · pointers,

- · records,

- files

- Various control structures (if, case, when ... else, with ... select etc.)

- Loops (loop, for, while)

- Functions and procedures

- ...

BF - ES - 38 -

## **Functions and procedures**

- Apart from entities / architectures there are also functions and procedures in the usual (software) sense.

- Functions are typically used for providing conversion between data types or for defining operators on userdefined data types.

- Procedures may have parameters of directions in, out and inout.

- in comparable to call by value,

- out for providing results,

- inout comparable to call by reference.

BF - ES - 39 -

## **Example**

```

architecture RTL of TEST is

function BOOL2BIT (BOOL: boolean) return bit is

begin

if BOOL then return '1'; else return '0'; end if;

end BOOL2BIT;

procedure EVEN_PARITY (

signal D: in bit_vector(7 downto 0);

signal PARITY: out bit ) is

variable temp: bit;

begin

....

end;

signal DIN: bit_vector(7 downto 0);

signal BOOL1: boolean;

signal BIT1, PARITY: bit;

begin

do_it: process (BOOL1, DIN)

begin

BIT1 <= BOOL2BIT(BOOL1);

EVEN_PARITY(DIN, PARITY);

end process;

....

end;

```

BF - ES - 40 -

## **Parameterized hardware**

- Conditional component instantiation with if ... generate construct.

- Iterative component instantiation with for ... generate construct.

- Parameterized design with **generic** parameters.

BF - ES - 41 -

#

```

bit5 <u>T(4)</u>

bit4 <u>T(3)</u>

bit3 <u>T(2)</u>

bit2 \frac{T(1)}{\text{bit1}} \frac{T(0)}{\text{bit0}}

CLK -

architecture RTL1 of SHIFT8 is

component DFF

port ( RSTn, CLK, D: in std_logic;

Q

: out std_logic );

end component;

signal T: std_logic_vector(6 downto 0);

begin

bit7 : DFF

port map (RSTn => RSTn, CLK => CLK,

D => SI, Q => T(6);

port map (RSTn => RSTn, CLK => CLK,

D => T(6), Q => T(5));

port map (RSTn, CLK, T(5), T(4));

port map (RSTn, CLK, T(1), T(0));

port map (RSTn, CLK, T(0), S0);

BF - ES

end RTL1;

- 43 -

```

```

Example: 1024-bit shift register

architecture RTL2 of SHIFT1024 is

component DFF

port (RSTn, CLK, D: in std_logic;

Q : out std_logic);

end component;

signal T: std_logic_vector(1022 downto 0);

begin

g0: for i in 1023 downto 0 generate

g1: if (i = 1023) generate

bit1023: DFF port map (RSTn,CLK,SI,T(1022));

end generate;

g2: if (i>0) and (i<1023) generate

bitm: DFF port map (RSTn,CLK,T(i),T(i-1));

end generate;

g3: if (i=0) generate

bit0: DFF port map (RSTn,CLK,T(0),S0);

end generate;

end generate;

end generate;

```

```

Example: n-bit shift register

entity SHIFTn is

generic (n: positive);

port (RSTn, CLK, SI: in std_logic;

SO: out std_logic);

architecture RTL3 of SHIFTn is

component DFF

port ( RSTn, CLK, D: in std_logic;

end SHIFTn;

: out std_logic );

end component;

signal T: std_logic_vector(n-2 downto 0);

begin

g0: for i in n-1 downto 0 generate

g1: if (i = n-1) generate

bit_high: DFF port map (RSTn,CLK,SI,T(n-2));

end generate;

g2: if (i>0) and (i<n-1) generate

bitm : DFF port map (RSTn,CLK,T(i),T(i-1));

end generate;

g3: if (i=0) generate

bit0: DFF port map (RSTn,CLK,T(0),S0);

end generate;

end generate;

end RTL3;

BF - ES

- 45 -

```

## **Example: n-bit shift register**

Component instantiation

BF - ES

23

- 46 -

## **Recursive descriptions**

- If parametrized hardware is described recursively, then

- generic-parameters,

- if ... generate-constructs for conditional component instantiation and

- recursive component instantiation are used.

- Example: Conditional Sum Adder

BF - ES - 47 -

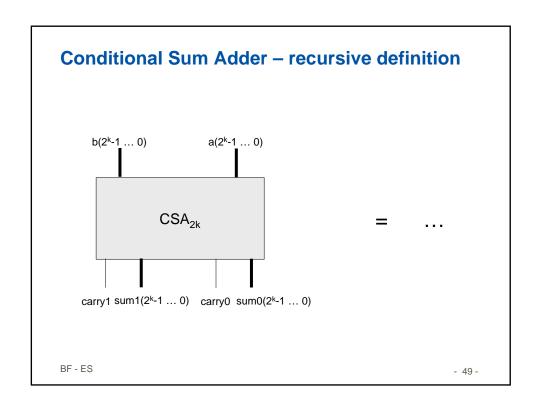

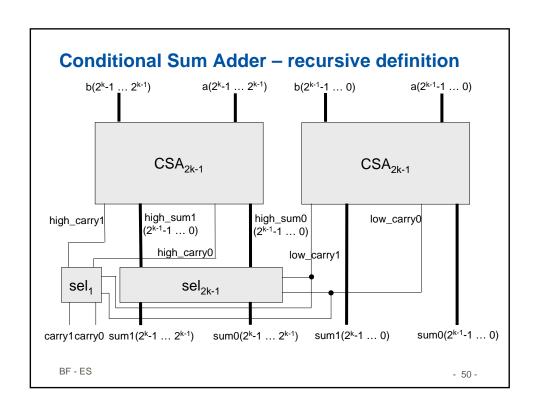

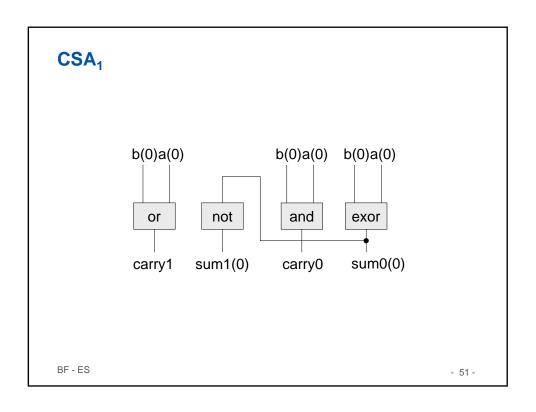

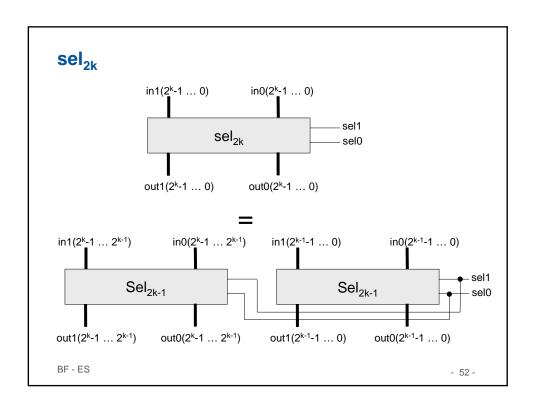

## **Conditional Sum Adder**

A conditional sum adder CSA<sub>n</sub> computes both sum and sum + 1 of two operand, i.e., it implements a Boolean function

```

\begin{split} & +_n \colon \boldsymbol{B}^{2n} \to \boldsymbol{B}^{2n+2} \;, \\ & (a_{n-1}, \, ..., \, a_0 \;, \, b_{n-1}, \, ..., \, b_0 \;) \to \\ & (\text{carry1}, \, \text{sum1}_{n-1}, \, ..., \, \text{sum1}_0, \, \text{carry0}, \, \text{sum0}_{n-1}, \, ..., \, \text{sum0}_0) \; \text{with} \\ & < \text{carry0}, \, \text{sum0}_n \; ... \; \text{sum0}_0 > = < a_{n-1} \; ... \; a_0 > + < b_{n-1} \; ... \; b_0 > \\ & < \text{carry1}, \, \text{sum1}_n \; ... \; \text{sum1}_0 > = < a_{n-1} \; ... \; a_0 > + < b_{n-1} \; ... \; b_0 > + 1. \end{split}

```

- It can be realized by

- Two conditional sum adders CSA<sub>n/2</sub>

- One n/2-bit select circuit sel<sub>n/2</sub>

- One 1-bit select circuit sel<sub>1</sub>

- Let  $n = 2^k$ .

BF - ES - 48 -

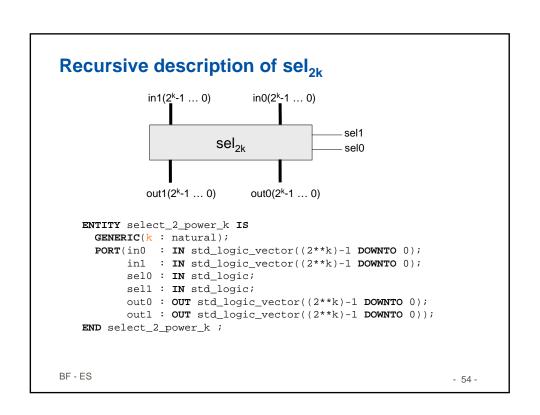

```

ARCHITECTURE netlist OF select_2_power_k IS

COMPONENT mux

PORT (ml, m0, sel : IN std_logic; res : OUT std_logic);

END COMPONENT;

COMPONENT select_2_power_k

GENERIC(k : natural);

PORT(in0 : IN std_logic_vector(2**k-1 DOWNTO 0);

inl : IN std_logic_vector(2**k-1 DOWNTO 0);

sel0 : IN std_logic;

sel1 : IN std_logic;

out0 : OUT std_logic;

out1 : OUT std_logic_vector(2**k-1 DOWNTO 0);

out1 : OUT std_logic_vector(2**k-1 DOWNTO 0));

END COMPONENT;

...

BF-ES

```

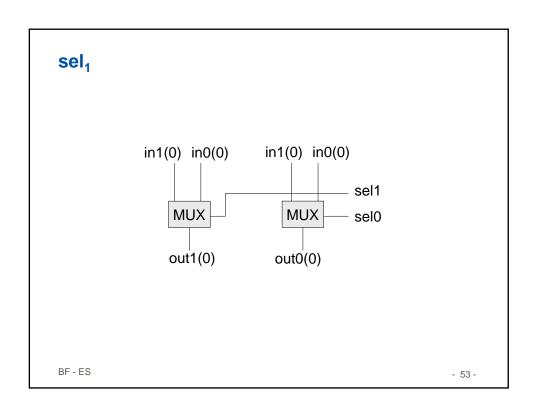

```

in1(0) in0(0)

in1(0) in0(0)

sel1

MUX

MUX

sel0

out1(0)

out0(0)

BEGIN

basisblock: IF k = 0 GENERATE

-- Erzeuge sel_1

mux1 : mux

PORT MAP(in1(0), in0(0), sel1, out1(0));

mux0 : mux

PORT MAP(in1(0), in0(0), sel0, out0(0));

END GENERATE;

- 56 -

```

```

in1(2<sup>k-1</sup>-1 ... 0)

in0(2<sup>k-1</sup>-1 ... 0)

in1(2<sup>k</sup>-1 ... 2<sup>k-1</sup>)

in0(2^{k-1}...2^{k-1})

sel1

Sel<sub>2k-1</sub>

Sel<sub>2k-1</sub>

sel0

out1(2<sup>k</sup>-1 ... 2<sup>k-1</sup>)

out0(2^{k}-1 ... 2^{k-1})

out1(2<sup>k-1</sup>-1 ... 0)

out0(2k-1-1 ... 0)

recursion: IF k > 0 GENERATE

sel_high : select_2_power_k

GENERIC MAP(k => k-1)

PORT MAP (in0 => in0(2**k-1 DOWNTO 2**(k-1)),

in1 = in1(2**k-1 DOWNTO 2**(k-1)),

sel0 => sel0, sel1 => sel1,

out0 => out0(2**k-1 DOWNTO 2**(k-1)),

out1 => out1(2**k-1 DOWNTO 2**(k-1)));

sel_low : select_2_power_k

GENERIC MAP(k => k-1)

PORT MAP (in0 => in0(2**(k-1)-1 DOWNTO 0),

in1 => in1(2**(k-1)-1 DOWNTO 0),

sel0 => sel0, sel1 => sel1,

out0 => out0(2**(k-1)-1 DOWNTO 0),

out1 => out1(2**(k-1)-1 DOWNTO 0));

END GENERATE;

END netlist;

- 57 -

```

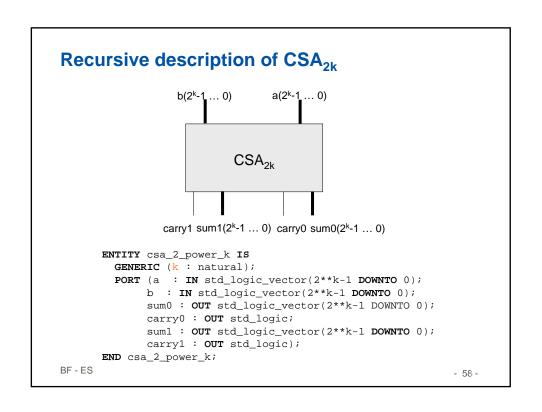

```

ARCHITECTURE csa_netlist OF csa_2_power_k IS

COMPONENT and2

PORT (a, b : IN std_logic; y : OUT std_logic);

END COMPONENT;

COMPONENT xor2

PORT (a, b : IN std_logic; y : OUT std_logic);

END COMPONENT;

COMPONENT or2

PORT (a, b : IN std_logic; y : OUT std_logic);

END COMPONENT;

COMPONENT inv

PORT (a : IN std_logic; y : OUT std_logic);

END COMPONENT;

...

BF-ES

```

```

COMPONENT select_2_power_k

GENERIC (k : natural);

PORT(in0 : IN std_logic_vector(2**k-1 DOWNTO 0);

in1 : IN std_logic_vector(2**k-1 DOWNTO 0);

sel0 : IN std_logic;

sel1 : IN std_logic;

out0 : OUT std_logic_vector(2**k-1 DOWNTO 0);

out1 : OUT std_logic_vector(2**k-1 DOWNTO 0));

END COMPONENT;

COMPONENT csa_2_power_k

GENERIC (k : natural);

sum0 : OUT std_logic_vector(2**k-1 DOWNTO 0);

carry0 : OUT std_logic;

sum1 : OUT std_logic_vector(2**k-1 DOWNTO 0);

carry1 : OUT std_logic);

END COMPONENT;

. . .

BF - ES

- 60 -

```

```

b(0) a(0)

b(0) a(0)

b(0) a(0)

not

and

or

exor

. . .

sum1(0)

carry0

sum0(0)

carry1

BEGIN

one_bit: IF k = 0 GENERATE

SIGNAL int0 : std_logic;

BEGIN

exor_cell : xor2

PORT MAP(b(0), a(0), int0);

sum0(0) <= int0;

inv_cell : inv

PORT MAP(int0, sum1(0));

and_cell : and2

PORT MAP(b(0), a(0), carry0);

or_cell : or2

PORT MAP(b(0), a(0), carryl);

END GENERATE;

. . .

BF - ES

- 61 -

```

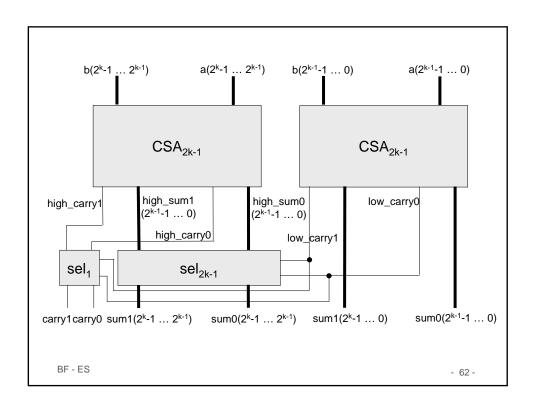

```

more_bit: IF k > 0 GENERATE

SIGNAL high_sum0 : std_logic_vector(2**(k-1)-1 DOWNTO 0);

SIGNAL high_sum1 : std_logic_vector(2**(k-1)-1 DOWNTO 0);

SIGNAL high_carry0 : std_logic_vector(0 DOWNTO 0);

SIGNAL high_carry1 : std_logic_vector(0 DOWNTO 0);

SIGNAL carry_out0 : std_logic_vector(0 DOWNTO 0);

SIGNAL carry_out1 : std_logic_vector(0 DOWNTO 0);

SIGNAL low_carry0 : std_logic;

SIGNAL low_carry1 : std_logic;

BEGIN

csa_high : csa_2_power_k

GENERIC MAP(k => k-1)

PORT MAP(a => a(2**k-1) DOWNTO 2**(k-1)),

b \Rightarrow b(2**k-1 \text{ DOWNTO } 2**(k-1)),

sum0 => high_sum0, carry0 => high_carry0(0),

sum1 => high_sum1, carry1 => high_carry1(0));

csa_low : csa_2_power_k

GENERIC MAP(k => k-1)

PORT MAP(a => a(2**(k-1)-1) DOWNTO 0),

b = b(2**(k-1)-1 DOWNTO 0),

sum1 => sum1(2**(k-1)-1 DOWNTO 0), carry1 => low_carry1);

. . .

- 63 -

```

```

sel_sum : select_2_power_k

GENERIC MAP(k => k-1)

PORT MAP(in0 => high_sum0, in1 => high_sum1,

sel0 => low_carry0, sel1 => low_carry1,

out0 => sum0(2**k-1 DOWNTO 2**(k-1)),

out1 => sum1(2**k-1 DOWNTO 2**(k-1)));

sel_carry : select_2_power_k

GENERIC MAP (k => 0)

PORT MAP (in0 => high_carry0, in1 => high_carry1,

sel0 => low_carry0, sel1 => low_carry1,

out0 => carry_out0, out1 => carry_out1);

carry0 <= carry_out0(0);</pre>

carry1 <= carry_out1(0);</pre>

END GENERATE:

END csa_netlist;

BF - ES

- 64 -

```

#### **VHDL: Evaluation**

- Hierarchical specification by entities / architectures / components, (procedures and functions)

- no nested processes,

- No specification of non-functional properties,

- No object-orientation,

- Static number of processes,

- Complicated simulation semantics,

- May be too low level for initial, abstract specification of very large systems.

- Mainly used for hardware generation (but not necessarily!).

BF - ES - 65 -

## (Other) Languages and Models

- UML (Unified Modelling Language) [Rational 1997]

"systematic" approach to support the first phases of the design process

- UML 1.xx not designed for embedded systems

UML 2.xx supports real-time applications

- several diagram types included

9 (UML 1.4)

13 (UML 2.0)

in particular variants of

StateCharts, MSCs, Petri Nets (called acticity diagrams)

BF - ES - 66 -

## **SDL**

- Language designed for specification of distributed systems.

- Dates back to early 70s,

- Formal semantics defined in the late 80s,

- Defined by ITU (International Telecommunication Union):

Z.100 recommendation in 1980

Updates in 1984, 1988, 1992, 1996 and 1999

BF - ES - 67 -

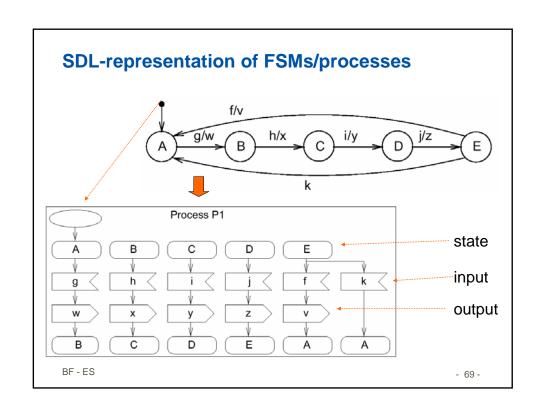

#### SDL

- Provides textual and graphical formats to please all users,

- Just like StateCharts, it is based on the CFSM model of computation; each FSM is called a process,

- However, it uses message passing instead of shared memory for communications,

- SDL supports operations on data.

BF - ES - 68 -

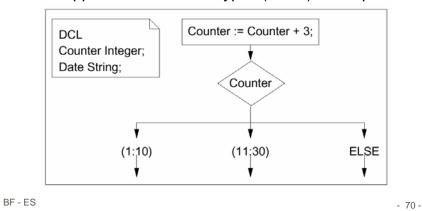

## **Operations on data**

- Variables can be declared locally for processes.

- Their type can be predefined or defined in SDL itself.

- SDL supports abstract data types (ADTs). Examples:

## **Communication among SDL-FSMs**

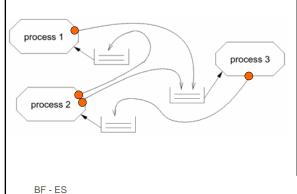

■ Communication between FSMs (or "processes") is based on message-passing, assuming a potentially indefinitely large FIFO-queue.

- Each process fetches next entry from FIFO,

- checks if input enables transition,

- if yes: transition takes place,

- if no: input is ignored (exception: SAVEmechanism).

- 71 -

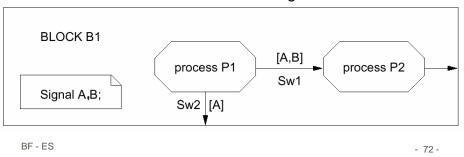

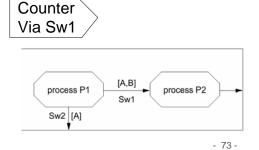

## **Process interaction diagrams**

- Interaction between processes can be described in process interaction diagrams (special case of block diagrams).

- In addition to processes, these diagrams contain channels and declarations of local signals.

1. Through process identifiers:

Example: OFFSPRING represents identifiers of processes generated dynamically.

Counter TO OFFSPRING

2. Explicitly:

By including the channel name.

3. Implicitly:

If signal names imply channel names (B  $\rightarrow$  Sw1)

BF - ES

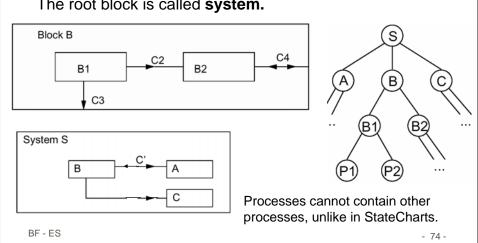

## **Hierarchy in SDL**

Process interaction diagrams can be included in blocks. The root block is called system.

## **Application: description of network protocols** System Processor A Router Processor B Processor C C1 Block Processor C Block Processor A Block Processor B layer-n layer-n layer-n **Block Router** layer-2 layer-1 layer-1 layer-1 layer-1 BF - ES - 75 -

## **Java**

Java 2 Micro Edition (J2ME)

CardJava

Real-time specification for Java (JSR-1), see //www.rtj.org

## **SystemC**

Attempts to describe software and hardware in the same language. Easier said than implemented.

Various C dialects used for hardware description.

BF - ES - 76 -

## **Verilog**

- HW description language competing with VHDL

- More popular in the US (VHDL common in Europe)

## **SystemVerilog**

Additional language elements for modeling behavior

BF - ES

- 77 -

## SpecC [Gajski, Dömer et. al. 2000]

SpecC is based on the clear separation between communication and computation. Enables "plug-and-play" for system components; models systems as hierarchical networks of behaviors communicating through channels

BF - ES - 78 -

## Many other languages

- Pearl: Designed in Germany for process control applications. Dating back to the 70s. Popular in Europe.

- Chill: Designed for telephone exchange stations.

Based on PASCAL.

- IEC 60848, STEP 7: Process control languages using graphical elements

BF - ES - 79 -

## Other languages (2)

- LOTOS, Z: Algebraic specification languages

- **Silage**: functional language for digital signal processing.

- Rosetta: Efforts on new system design language

- Esterel: reactive language; synchronous;

all reactions are assumed to be in 0 time;

communication based on ("instantaneous") broadcast;

//www.esterel-technologies.com

BF - ES - 80 -

## **Language Comparison**

| Language    | Behavioral<br>Hierarchy | Structural<br>Hierarchy | Programming<br>Language<br>Elements | Exceptions<br>Supported | Dynamic<br>Process<br>Creation |

|-------------|-------------------------|-------------------------|-------------------------------------|-------------------------|--------------------------------|

| StateCharts | +                       | -                       | -                                   | +                       | -                              |

| VHDL        | +                       | +                       | +                                   | -                       | -                              |

| SpecCharts  | +                       | -                       | +                                   | +                       | -                              |

| SDL         | +-                      | +-                      | +-                                  | -                       | +                              |

| Petri nets  | -                       | -                       | -                                   | -                       | +                              |

| Java        | +                       | -                       | +                                   | +                       | +                              |

| SpecC       | +                       | +                       | +                                   | +                       | +                              |

| SystemC     | +                       | +                       | +                                   | - (2.0)                 | - (2.0)                        |

| ADA         | +                       | -                       | +                                   | +                       | +                              |

BF - ES - 81 -