### REVIEW **Saturating arithmetic** Returns largest/smallest number in case of over/underflows Example: 0111 а 1001 b standard wrap around arithmetic (1)0000saturating arithmetic 1111 (a+b)/2: correct 1000 wrap around arithmetic 0000 0111, almost correct saturating arithmetic + shifted Appropriate for DSP/multimedia applications: • No timeliness of results if interrupts are generated for overflows • Precise values less important • Wrap around arithmetic would be worse. BF - ES - 8 -

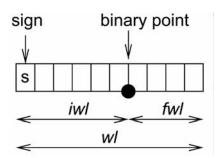

# **Fixed-point arithmetic**

- Less significant digits are chopped off.

- Example:  $x=0.5 \times 0.125 + 0.25 \times 0.125 = 0.0625 + 0.03125 = 0.09375$  For iwl=1 and fwl=3 decimal digits, the less significant digits are automatically chopped off: x=0.093 Like a floating point system with numbers  $\in$  (-1..1), with no stored exponent.

- Appropriate for DSP/multimedia applications (well-known value ranges).

BF - ES

- 9 -

# **Real-time capability**

- Timing behavior has to be predictable Features that cause problems:

- Unpredictable access to shared resources

- Caches with difficult to predict replacement strategies

- Unified caches (conflicts betw. instructions and data)

- Pipelines with difficult to predict stall cycles ("bubbles")

- Unpredictable communication times for multiprocessors

- Branch prediction, speculative execution

- · Interrupts that are possible any time

- · Memory refreshes that are possible any time

- Instructions that have data-dependent execution times

- Trying to avoid as many of these as possible.

BF - ES

- 10 -

[Dagstuhl workshop on predictability, Nov. 17-19, 2003]

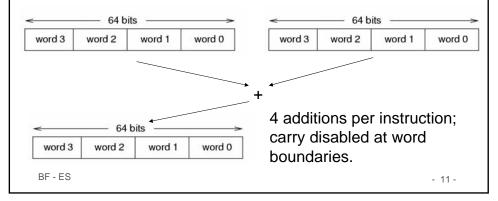

# **Multimedia-Instructions/Processors**

- Multimedia instructions exploit that many registers, adders etc are quite wide (32/64 bit),

- whereas most multimedia data types are narrow

(e.g. 8 bit per color, 16 bit per audio sample per channel)

- 2-8 values can be stored per register and added. E.g.:

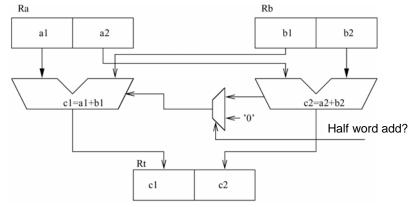

### Early example: HP precision architecture (hp PA)

Half word add instruction **HADD**:

Optional saturating arithmetic.

Up to 10 instructions can be replaced by HADD.

BF - ES - 12 -

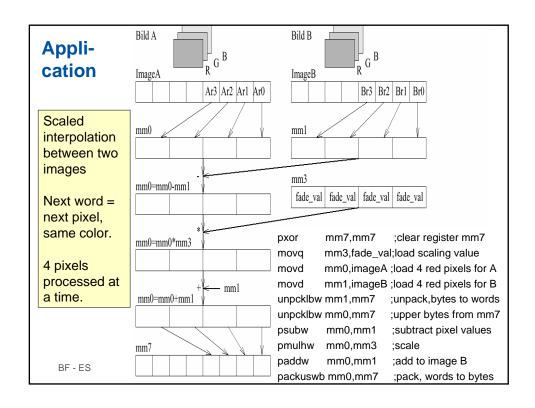

# **Pentium MMX-architecture (1)**

64-bit vectors representing 8 byte encoded, 4 word encoded or 2 double word encoded numbers.

wrap around/saturating options.

Multimedia registers mm0 - mm7, consistent with floating-point registers (OS unchanged).

| Options      | Comments                                          |

|--------------|---------------------------------------------------|

| wrap around, | addition/subtraction of                           |

| saturating   | bytes, words, double words                        |

|              | Result= "1111" if true, "0000" otherwise          |

|              | Result= "1111" if true, "0000" otherwise          |

|              | multiplication, 4*16 bits, least significant word |

|              | multiplication, 4*16 bits, most significant word  |

|              | wrap around,                                      |

BF - ES - 13 -

# Pentium MMX-architecture (2)

| Psra[w/d]<br>Psll[w/d/q]<br>Psrl[w/d/q] | No. of positions in register or instruction | Parallel shift of words, double words or 64 bit quad words |

|-----------------------------------------|---------------------------------------------|------------------------------------------------------------|

| Punpckl[bw/wd/dq]                       |                                             | Parallel unpack                                            |

| Punpckh[bw/wd/dq]                       |                                             | Parallel unpack                                            |

| Packss[wb/dw]                           | saturating                                  | Parallel pack                                              |

| Pand, Pandn                             |                                             | Logical operations on 64 bit words                         |

| Por, Pxor                               |                                             |                                                            |

| Mov[d/q]                                |                                             | Move instruction                                           |

BF - ES - 14 -

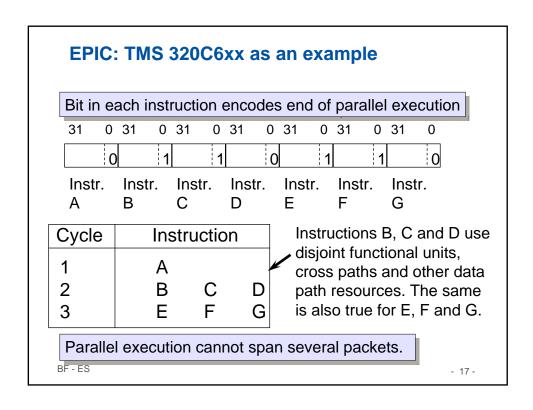

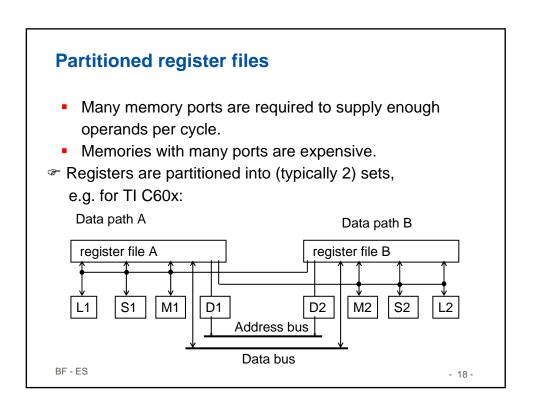

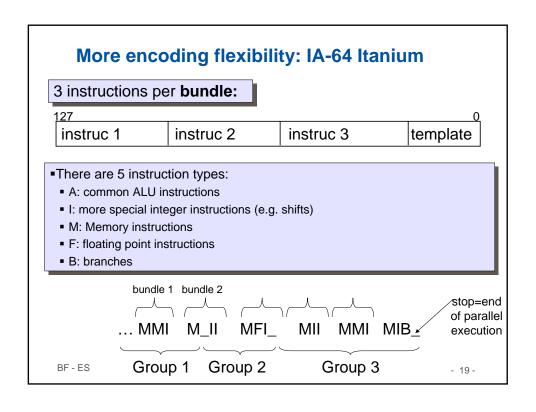

# Very long instruction word (VLIW) architectures

- Very long instruction word ("instruction packet") contains several instructions, all of which are assumed to be executed in parallel.

- Compiler is assumed to general these "parallel" packets

- Complexity of finding parallelism is moved from the hardware (RISC/CISC processors) to the compiler;

Ideally, this avoids the overhead (silicon, energy, ..) of identifying parallelism at run-time.

- A lot of expectations into VLIW machines

- Explicitly parallel instruction set computers (EPICs) are an extension of VLIW architectures: parallelism detected by compiler, but no need to encode parallelism in 1 word.

BF - ES - 16 -

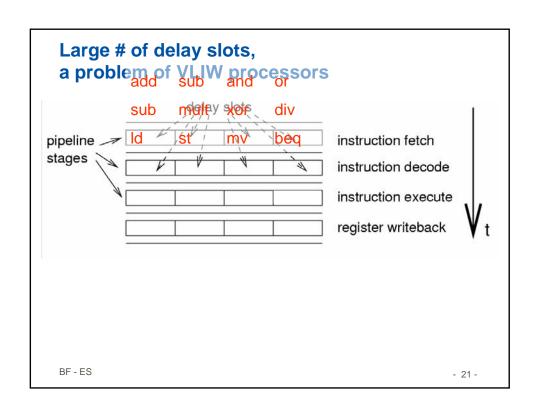

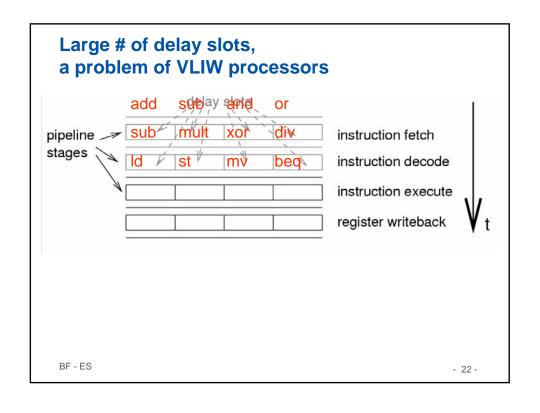

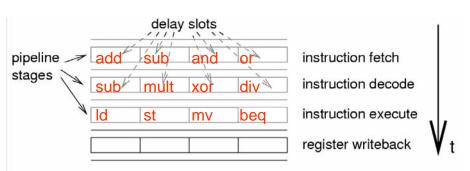

# Large # of delay slots, a problem of VLIW processors

The execution of many instructions has been started before it is realized that a branch was required.

Nullifying those instructions would waste compute power

- Executing those instructions is declared a feature, not a bug.

- How to fill all "delay slots" with useful instructions?

- Avoid branches wherever possible.

BF - ES - 23 -

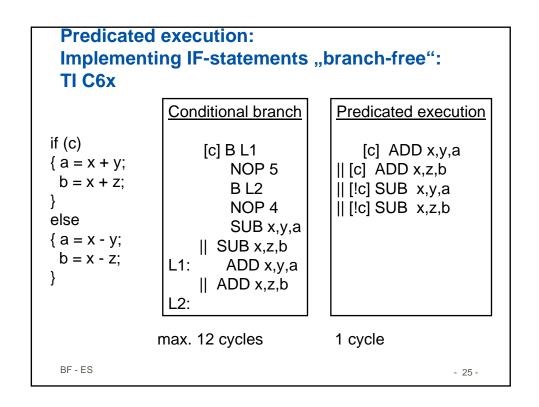

# Predicated execution: Implementing IF-statements "branch-free"

Conditional Instruction "[c] I" consists of:

- condition c

- instruction I

c = true => I executed c = false => NOP

BF - ES - 24 -

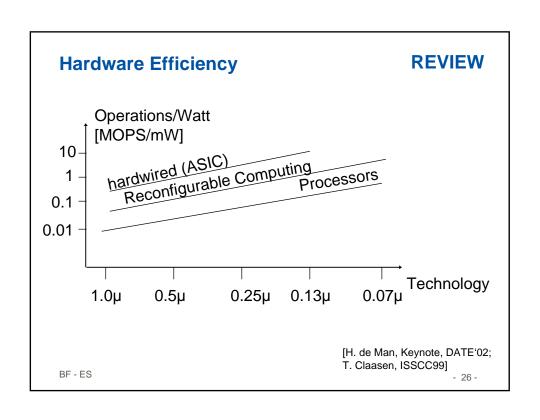

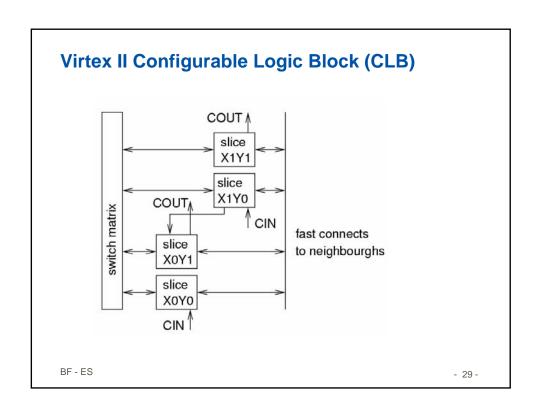

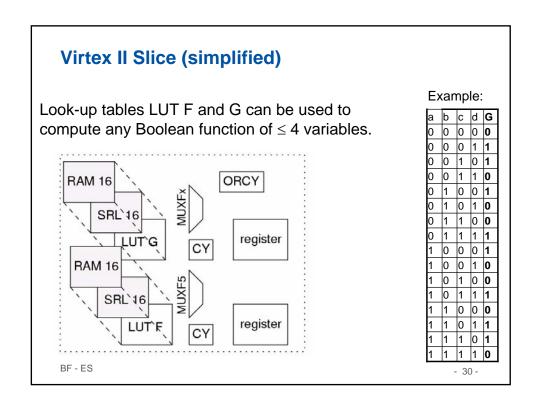

# **Reconfigurable Logic**

- •Full custom chips may be too expensive, software too slow.

- Combine the speed of HW with the flexibility of SW

- THW with programmable functions and interconnect.

- Use of configurable hardware; common form: field programmable gate arrays (FPGAs)

- Applications: bit-oriented algorithms like

- encryption,

- fast "object recognition" (medical and military)

- Adapting mobile phones to different standards.

- Very popular devices from

- XILINX (XILINX Vertex II are recent devices)

- Actel, Altera and others

BF - ES - 27 -

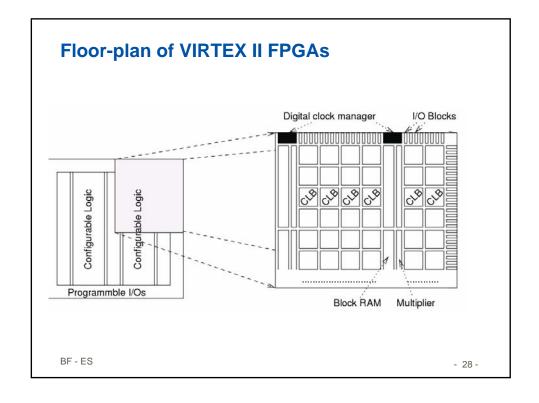

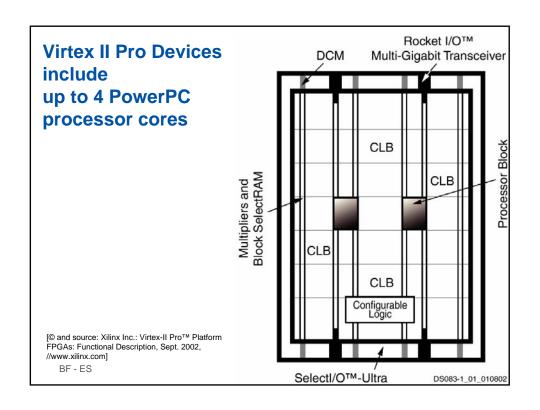

# **Number of resources** available in Virtex II Pro devices

Table 16: Virtex-II Pro Logic Resources Available in All CLBs

| Device   | CLB Array:<br>Row x<br>Column | Number<br>of<br>Slices | Number of LUTs | Max Distributed<br>SelectRAM+ or<br>Shift Register<br>(bits) | Number of Flip-Flops | Number of<br>Carry Chains <sup>(1)</sup> | Number<br>of SOP<br>Chains <sup>(1)</sup> |

|----------|-------------------------------|------------------------|----------------|--------------------------------------------------------------|----------------------|------------------------------------------|-------------------------------------------|

| XC2VP2   | 16 x 22                       | 1,408                  | 2,816          | 45,056                                                       | 2,816                | 44                                       | 32                                        |

| XC2VP4   | 40 x 22                       | 3,008                  | 6,016          | 96,256                                                       | 6,016                | 44                                       | 80                                        |

| XC2VP7   | 40 x 34                       | 4,928                  | 9,856          | 157,696                                                      | 9,856                | 68                                       | 80                                        |

| XC2VP20  | 56 x 46                       | 9,280                  | 18,560         | 296,960                                                      | 18,560               | 92                                       | 112                                       |

| XC2VP30  | 80 x 46                       | 13,696                 | 27,392         | 438,272                                                      | 27,392               | 92                                       | 160                                       |

| XC2VP40  | 88 x 58                       | 19,392                 | 38,784         | 620,544                                                      | 38,784               | 116                                      | 176                                       |

| XC2VP50  | 88 x 70                       | 23,616                 | 47,232         | 755,712                                                      | 47,232               | 140                                      | 176                                       |

| XC2VP70  | 104 x 82                      | 33,088                 | 66,176         | 1,058,816                                                    | 66,176               | 164                                      | 208                                       |

| XC2VP100 | 120 x 94                      | 44,096                 | 88,192         | 1,411,072                                                    | 88,192               | 188                                      | 240                                       |

| XC2VP125 | 136 x 106                     | 55,616                 | 111,232        | 1,779,712                                                    | 111,232              | 212                                      | 272                                       |

Notes:

1. The carry-chains and SOP chains can be split or cascaded. BF - ES

[© and source: Xilinx Inc.: Virtex-II Pro™ Platform FPGAs: Functional Description, Sept. 2002, //www.xilinx.com]

# Interconnect 24 Horizontal Long Lines Hierarchical Routing Resources 24 Vertical Long Lines 120 Horizontal Hex Lines 120 Vertical Hex Lines 40 Horizontal Double Lines 40 Vertical Double Lines 16 Direct Connections (total in all four directions) 8 Fast Connects BF - ES - 32 -

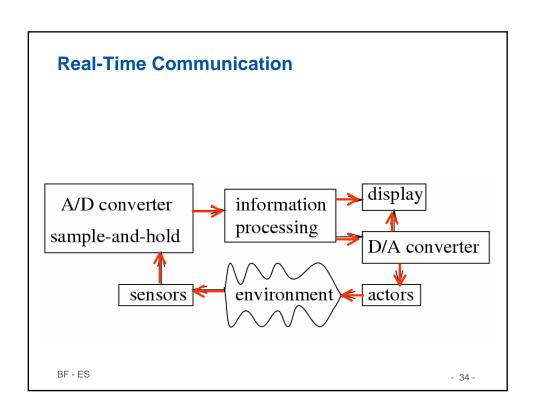

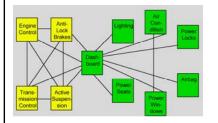

### Advantages of standardized communication media

- 1. Modular system development, support and evolution

- 2. Single network vs. wiring harness

- Difficult to connect the wrong cable if there is only one

- 3. Low per-node cost permits repair by replacing entire node

- Diagnosis by bus snooping

- 4. More flexible physical allocation

BF - ES - 35 -

# **Requirements: Protocol Latency**

- Low and almost constant (i.e., reliable) communication

- Small latency = rapid communication, low distribution overhead

- Low jitter = reliable correspondence between actual causal and observed temporal dependency

- Simultaneous or phase-constant delivery upon multicast

- strict correlation of various distributed real-time images of dynamically evolving entities

BF - ES - 36 -

# **Requirements: Support for Composability**

- Temporal encapsulation of nodes

- WCET analysis, scheduling, etc. are simplified if pace of program execution on nodes is independent of communication events

- Analysis of protocol latency, jitter, etc. is simplified if communication is under autonomous control of the communication network

- Established solution: computer/network interface (CNI) or I/O coprocessor autonomously performing message transfers

- Assume/guarantee between servers and clients

- Server must be protected from burst loads; otherwise, it will be unable to fulfill its commitment

- Established solution: design by contract server delivers reliable service whenever clients stick to their contract concerning activation patterns

- Communication layer enforcing the contract simplifies design through separation of concerns

BF - ES - 37 -

# **Requirements: Flexibility**

- Multiple configurations

- Customizable products, e.g. different equipment levels and optional equipment in cars, require spare and/or reassignable channel capacity.

- Operational modes of the overall system: startup, normal operation, emergency, ...

- Interleaving communications with extraordinary resource constraints:

e.g., airbag deployment

BF - ES - 38 -

# **Requirements: Error Detection**

- Dependable service of communication system

- Errors should be detected and corrected without seriously increasing communication jitter.

- Unconcealable errors have to be reported asap to the affected communication partners to allow them to implement error masking.

- Detection of node errors

- Node errors should be detected by communication system.

- Erratic nodes should be isolated from the network in order to implement a failsilent policy.

- Communication partners relying on an erratic node's service have to be informed about lack of service (with low latency).

- Recovered nodes should be reintegrated into network.

- Support of end-to-end acknowledgements

- End-to-end acknowledgement permits fault detection over a whole causal chain.

- Correlating requests and acknowledgements is difficult / impossible if end-to-end latency / jitter is larger than minimum separation between requests.

BF - ES - 39 -

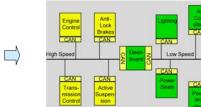

# **End-to-end Acknowledgement**

- RT entity: an "object" whose state is dynamically evolving over real time

- RT image: an image of the state of such an "object", as obtained through measurements, communicated values/events, ...

BF - ES - 40 -

20

### Flow Control: Rationale

In any communication system, there is an inherent asymmetry between sender and receiver upon overload:

- 1. A sender can continue producing messages at its own pace if the receiver is faster than its own pace.

- 2. A receiver may become overloaded and fail to provide service if sender is faster than its own pace.

The receiver needs an extra instrument: flow control

BF - ES - 41 -

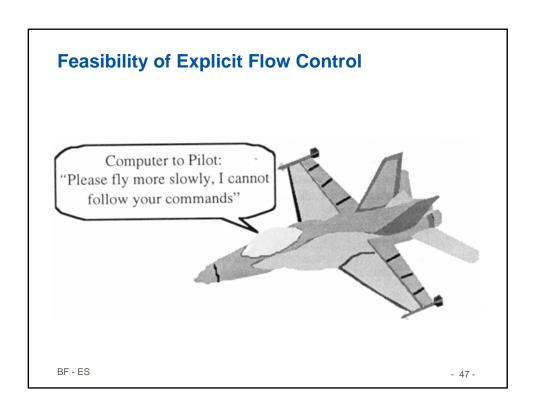

# **Explicit Flow Control**

...puts the senders rate of transmission into the control of the receiver, e.g. through

- 1. explicit control messages being sent back:

- acknowledgements,

- start/stop signals inhibiting communication whenever undesired,

- maskable interrupts

- 2. third-party-controlled or hidden channels:

- sender observes RT entities that are in the SoC of the receiver to determine completion of receiver's response to its message.

BF - ES - 42 -

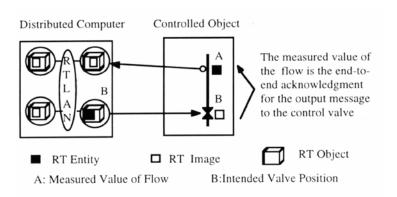

# **Explicit Flow Ctrl.: Fault Tolerance**

- Error detection and masking is typically implemented by the sender:

- Senders waits for acknowledgement (or other causal consequence of message).

- When absence of that causal consequence becomes permanent (error detection), it retries communication (an attempt on error concealment). ("becomes permanent" means can be definitely asserted due to maximum latency having expired)

- 3. In hard real-time systems, number of retries has to be bounded: Receiver (and further affected parties) are informed.

BF - ES - 43 -

# **Implicit Flow Control**

- ...subjects message flow to a contract, where obedience to the contract can be locally controlled by sender:

- 1. A (possibly situation-dependent) a priori rate/temporal pattern is agreed upon

- at design time, or

- at startup (example: modems exchanging test-"pings".)

- 2. Senders commits itself to send only at agreed time instants.

- 3. No acknowledgements are sent (normally).

- 4. Error detection is implemented by receiver, which detects noncontractual message streams.

With implicit flow control, communication is typically unidirectional.

BF - ES - 45 -

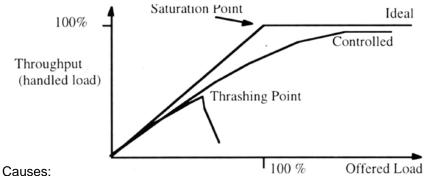

# Thrashing ...occurs when throughput is nonmonotic in load:

- Increasing error rates (e.g. due to higher collision probability on communication network) reduce operational / error recovery ratio.

- Overhead for operating system services (e.g. scheduling) may increase.

BF - ES - 46 -

# Flow Control Mechanisms vs. Hard Real-Time

| Characteristic                         | Explicit flow ctrl.                                  | Implicit flow ctrl.                                   | Requirements of<br>hard RT                           |  |

|----------------------------------------|------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------|--|

| Control signal                         | Receiver's SoC has to include sender's transmissions | Transmission ctrl. is effected by progression of time | Receiver's ctrl. of<br>sender may be very<br>limited |  |

| Error detec-<br>tion                   | At sender                                            | At receiver                                           | ?                                                    |  |

| Prone to thrashing                     | Yes                                                  | No                                                    | Predictability dictates avoidance of thrashing       |  |

| Multicasting Intricate and error prone |                                                      | Straightforward                                       | Often required                                       |  |

|                                        |                                                      |                                                       | [After H. Kopetz]                                    |  |

Implicit flow control is often more appropriate.

BF - ES - 48 -

### No free lunch:

- Fundamental tension:

- Small latency for important nodes/ messages vs.

- Sufficient and consistent service for less important nodes/messages.

- Measures:

- Local priority:

- Each node (or its communication sub-system) can implement a policy of which message(s) shall go to the network when the node gets access

- Can be static priority/dynamic priority/round robin/...

- Global priority:

- The network (and/or the node set) needs to implement policy for which node gets access when

- Can be static node priority/dynamic node priority/round robin/...

BF - ES - 49 -

# **Bus Master Approach to Coordination**

Bus master polls for messages:

- Master sends polling messages and waits for response

- Error detection:

- 1. unresponsive or slow slave

- Master uses timeout based on worst-case response time when waiting for response

- Protocol fails/is retried when timeout expires

- 2. faulty master

- As the master produces some heartbeat on the network, this is detectable

- Use stand-by techniques (redundant masters)

BF - ES - 50 -

# **Bus Master Approach to Coordination**

### Slave-to-slave communication

- Master polls a willing-to-send slave

- Slave transmits message only when polled

- Potential recipients listen to bus traffic

## Examples

MIL-STD-1553B, 1773

Profibus (and many other fieldbusses)

BF - ES - 51 -

# **Bus Master Approach to Coordination**

### Advantages

- Simple to implement, therefore historically very popular

- Bounded latency (if individual message length is constrained)

- Easy to make adaptive versions that adapt to different operational modes of the system

### Disadvantages

- Centralized master detrimental to fault tolerance

- Polling consumes bandwidth

- Number of nodes fixed during installation (or additional bandwith required for dynamic detection)

BF - ES - 52 -

# **TDMA - Time Division Multiplexed Access**

### Principle of operation:

- 1. All (operational) nodes agree on a global time frame via synchronisation

- Either some master node sends out a frame sync to synchronize clocks (requires FT mechanisms), or

- nodes use distributed clock synchronization

- 2. Progress of time is divided into TDMA rounds, within which the individual nodes have private time slots with different phase delay to star t of the round; the slots are non-overlapping

- 3. Each node transmits only during its private time slot

### Examples:

TTP

FlexRay

BF - ES - 53 -

# **TDMA - Time Division Multipl. Access**

### Advantages:

- Deterministic response time

- No polling overhead

- Easy to implement and to analyze

### Disadvantages:

- Private slots waste bandwith

- Need for global clock synchronisation

- Number of nodes and their worst-case message lengths need to be fixed a priori

- This leads to either designs using huge safety margins or to complex interference between node performance and TDMA setup (lacking separation of concerns between computation and communication)

BF - ES - 54 -

# **Carrier Sense Multiple Access (CSMA)**

### Operational principle:

If communication medium is idle then send a message (node decides on its own — no global authority)

### Problems:

- Multiple nodes may start almost synchronously, leading to collision on the medium

- Message may be crippled

- Message may be overwritten and thus not delivered

- If message delivery is vital (std. in ES) then collision has to be resolved

- Collision detection or collision avoidance, arbiting the bus such that at least one of the colliding messages is delivered uncrippled

BF - ES - 55 -

# **CSMA** with Detection (CSMA/CD)

### Operational principle

- Node waits for an idle channel before transmitting

- Collisions occur if two or more nodes start (almost) simultaneously

- If a collision is detected, the nodes stop transmitting

- After collision, the nodes back off a certain time, which varies from node to node

- Random assignment of backoff times (worst-case number of retries unbounded), or

- Systematic assignment, e.g. static assignment a priori (requires known number of nodes at design time)

### Examples

Ethernet/IEEE 802.3

LON, CEBus (home networks using power-line modulation)

BF - ES - 56 -

# **CSMA** with Detection

### Advantages:

- Small latency upon low traffic load

- Disruption-free network extension and reduction (with randomized backoff)

- Prioritization is possible by adequate assignment of backoff times (weak variant: probabilistic prioritization via different distributions of random backoff times)

- Extensive installed base and support

### Disadvantages:

- Inefficient under heavy loads prone to thrashing

- Designed for aperiodic traffic for periodic traffic, the necessity to explicitly tag messages with an identity (redundant in TDMA as the slot position conveys an identity) may cost bandwith

- Collision detection requires hardware

BF - ES - 57 -

# **CSMA** with Avoidance (CSMA/CA)

### Operational principle:

- 1. Bus arbitration resolves conflicts such that at least one messageis delivered uncrippled, or

- 2. bus arbitration avoids collisions altogether

Examples:

CAN

**ARINC 629**

BF - ES - 58 -

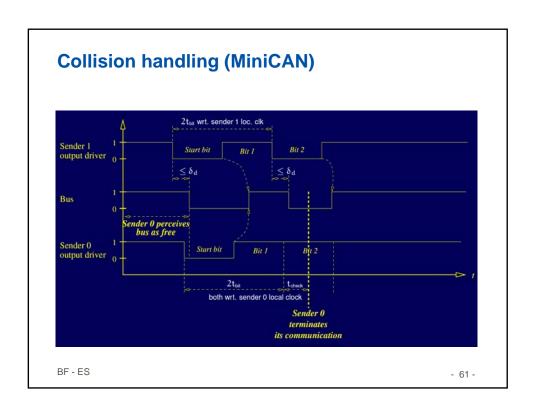

# The CAN bus

- two-valued bus:

- "dominant" (denoted 0 in the sequel) and

- "recessive" (denoted 1 in the sequel)

- if at least one sender sends a dominant bit (= 0) to the bus then the bus will go to "dominant" ( = 0) within  $\delta_d$  time units

- the bus will go to value "recessive" (= 1) if all senders have sent "recessive" for at least  $\delta_d$  time units.

Length  $t_{\mbox{\scriptsize bit}}$  of a bit slot has to be significantly larger than propagation delay along the bus and rise/fall times!

BF-ES - 59-

# Normal bustake-over (MiniCAN, 2-Bitident.) Sender 1 Output driver 0 Sender 3 perceives Sender 3 perceives bus as busy bus as free 3 local clock Bus 3 free 3 local clock Bus 41 Sender 3 perceives bus as busy bus as free 5 local clock Sender 3 Sender 3 perceives bus as busy bus as free 5 local clock Sender 3 Sender 3 perceives bus as busy bus as free 5 local clock Sender 3 Sender 3 perceives bus as busy bus as free 5 local clock Sender 3 Sender 3 perceives bus as busy bus as free 5 local clock Sender 3 Sender 3 perceives bus as busy bus as free 5 local clock Sender 3 Sender 3 perceives bus as busy bus as free 5 local clock Sender 3 Sender 3 perceives bus as busy bus as free 5 local clock Sender 3 Sender 3 perceives bus as busy bus as free 5 local clock Sender 3 Sender 3 perceives bus as busy bus as free 5 local clock Sender 3 Sender 3 perceives bus as busy bus as free 5 local clock Sender 3 Sender 3 perceives bus as busy bus as free 5 local clock

# **Message priority**

The rule governing early termination of message transfer introduces a priority order between messages: upon a collision, the sender with the lowest identity number wins control over the bus.

BF - ES - 62 -

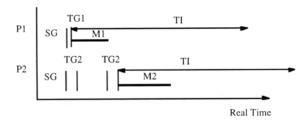

## **ARINC 629**

- Based on "waiting room" protocol:

- Each node is assigned a unique number of minislots that must elapse, with silence on the channel, before transmission

- Three (groups of) time-out parameters:

- 1. SG synchronization gap controlling access to the waiting room

- 2. TGi terminal gap, the personal time-out of node i

- 3. TI transmit interval preventing monopolization of channel TI > SG > max{TGi}

BF - ES

- 63 -

# **Token passing**

### Operational principle:

- Token value says which node is transmitting/should transmit next

- Only token holder is allowed to transmit

- Master/slave polling is a special form where token is passed by master and returned to master by slave

### Problems:

- Lost token

- duplicated/multiplicated token

BF - ES

- 64 -

# **Token passing**

### Advantages:

- Bounded latency

- More adaptive, i.e. higher bandwith under uneven load, than TDMA

— node can pass token immediately

- Token passing yields heartbeat supporting fault detection

### Disadvantages:

- Token passing induces unnecessary latencies under light traffic

- Fault tolerance intricate

BF - ES - 65 -

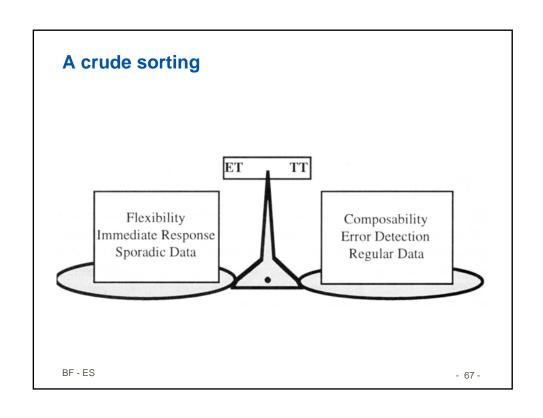

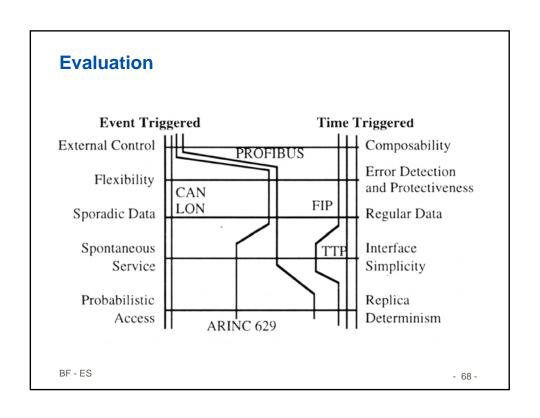

# **Event-Triggered vs. Time-Triggered**

- Event Triggered (ET):

- Computation/communication triggered by an external event

- Events are generated by (primarily) state changes in the environment Efficient — only do things when they need to be done; rest and save energy/cpu time/bandwidth/. . . otherwise

- High peak-load if multiple events happen at once

- Hard to analyze due to asynchronous nature of events

- Time Triggered (TT):

- Computation/communication triggered by progress of a system clock

- Events happen according to a fixed schedule Inefficient do things periodically, whether needed or not

- Enhanced analizability due to easily characterizable load, predictable interaction sequences, bus use, etc.

BF - ES - 66 -

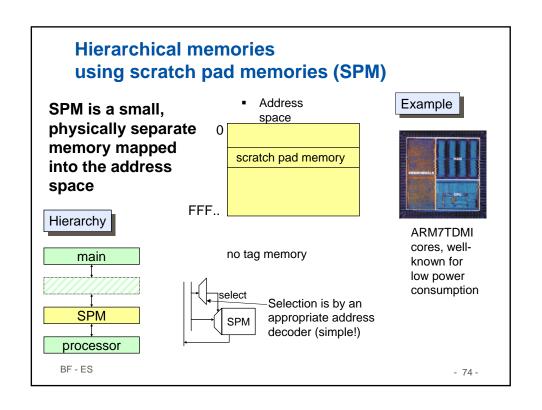

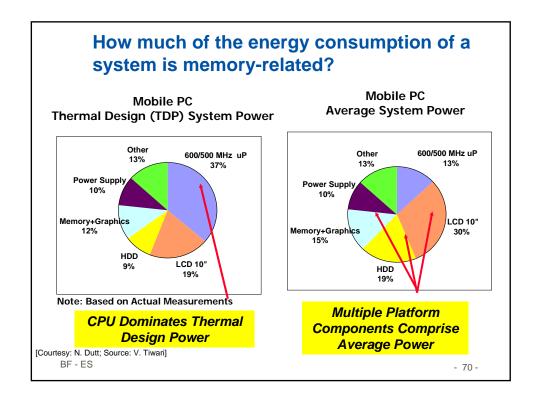

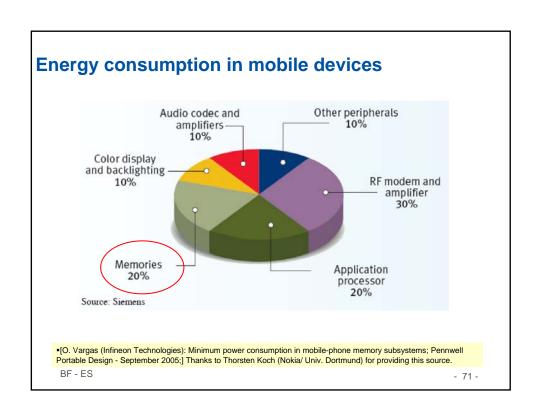

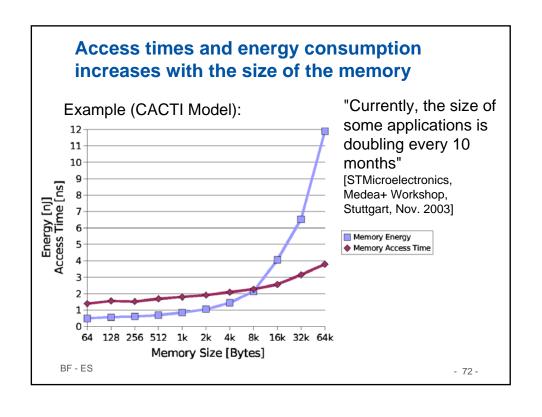

# **Memory**

- For the memory, efficiency is again a concern:

- speed (latency and throughput); predictable timing

- energy efficiency

- size

- cost

- other attributes (volatile vs. persistent, etc)

BF-ES - 69-

### Access-times will be a problem Speed gap between processing and main DRAM increases Performance early 60ties (Atlas): 8 page fault ~ 2500 instructions - 2002 (2 GHz μP): access to DRAM ~ 500 4 instructions penalty for cache miss about ≥ 2x same as for page fault in Atlas every 2 2 Similar problems for PCs and years DRAM (1.07 p.a **MPSoCs** [P. Machanik: Approaches to Addressing the 5 years 0 Memory Wall, TR Nov. 2002, U. Brisbane] BF - ES