# **Testing: Scope**

# **Testing** includes

- the application of test patterns to the inputs of the device under test (DUT) and

- the observation of the results.

More precisely, testing requires the following steps:

- 1. test pattern generation,

- 2. test pattern application,

- 3. response observation, and

- 4. result comparison (okay, not okay, inconclusive).

BF - ES - 2 -

### **Test pattern generation**

Test pattern generation typically

- considers certain fault models and

- generates patterns that enable a distinction between the faulty and the fault-free case.

- Coverage criteria shed light on the likeliness of instances of the fault type slipping through

BF - ES - 3 -

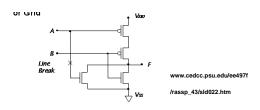

#### **Hardware Fault models**

Hardware fault models include:

- stuck-at fault model (net permanently connected to ground or V<sub>dd</sub>)

- stuck-open faults: for CMOS, open transistors can behave like memories

- delay faults: circuit is functionally correct, but the delay is not.

Break above results in a "memory effect" in the behavior of the circuit

With AB=10, there is not path from either VDD or VSS to the output

Fretains the previous value for some undetermined discharge time

BF - ES - 4 -

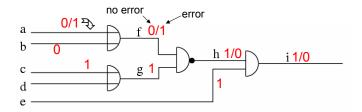

# Simple example

- Could we check for a stuck at one error at a (s-a-1(a))?

- Solution (just guessing):

- f='1' if there is an error

- $\Rightarrow$  a='0', b='0' in order to have f='0' if there is no error

- g='1' in order to propagate error

- c='1' in order to have g='1' (or set d='1')

- e='1' in order to propagate error

- i='1' if there is no error & i='0' if there is

BF - ES - 5 -

# Need to Deal With Two Copies of the Circuit Alternatively, use a multi-valued algebra of signal values for both good and faulty circuits. Faulty circuit September 2 Circuit Circuit Alternatively, use a multi-valued algebra of signal values for both good and faulty circuits.

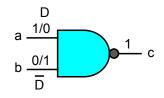

# Roth's 5-valued algebra (1966)

| Symbol | Alternative<br>Representation | Fault-free circuit | Faulty<br>Circuit |

|--------|-------------------------------|--------------------|-------------------|

| D      | 1/0                           | 1                  | 0                 |

| D      | 0/1                           | 0                  | 1                 |

| 0      | 0/0                           | 0                  | 0                 |

| 1      | 1/1                           | 1                  | 1                 |

| X      | X/X                           | X                  | X                 |

# **Function of NAND Gate**

|          |   | Input a |   |   |   |   |

|----------|---|---------|---|---|---|---|

| С        |   | 0       | 1 | X | D | D |

|          | 0 | 1       | 1 | 1 | 1 | 1 |

|          | 1 | 1       | 0 | Х | D | D |

| Input b  | X | 1       | X | X | Х | Х |

| <u> </u> | D | 1       | D | Х | D | 1 |

|          | D | 1       | D | Х | 1 | D |

- 8 -

BF - ES

Copyright Agrawal & Bushnell

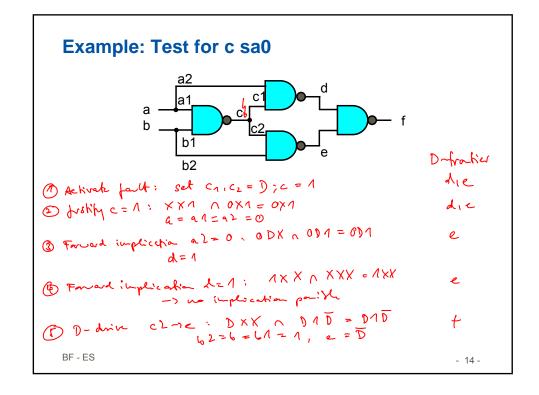

# **D-Algorithm**

- Use D-algebra

- Activate fault

- Place a D or  $\overline{D}$  at fault site

- Do justification, forward implication and consistency check for all signals

- Repeatedly propagate D-chain toward POs through a gate

- Do justification, forward implication and consistency check for all signals

- Backtrack if

- · A conflict occurs, or

- · D-frontier becomes empty

- Stop when

- · D or D at a PO, i.e., test found, or

- · If search exhausted without a test, then no test possible

BF - ES Copyright Agrawal & Bushnell - 9 -

#### **Definitions**

- Justification: Changing inputs of a gate if the present input values do not justify the output value.

- Forward implication: Determination of the gate output value, which is X, according to the input values.

- Consistency check: Verifying that the gate output is justifiable from the values of inputs, which may have changed since the output was determined.

- D-frontier: Set of gates whose inputs have a D or D, and the output is X.

BF - ES Copyright Agrawal & Bushnell - 10 -

# **Definition: Singular Cover**

- A singular cover defines the least restrictive inputs for a deterministic output value.

- Used for:

- Line justification: determine gate inputs for specified output.

- Forward implication: determine gate output.

Examples:

$XX0 \cap 110 = 110$  $0XX \cap 0X1 = 0X1$

| Singular covers | а | b | С |

|-----------------|---|---|---|

| SC-1            | 0 | Х | 1 |

| SC-2            | Х | 0 | 1 |

| SC-3            | 1 | 1 | 0 |

BF - ES

Copyright Agrawal & Bushnell

- 11 -

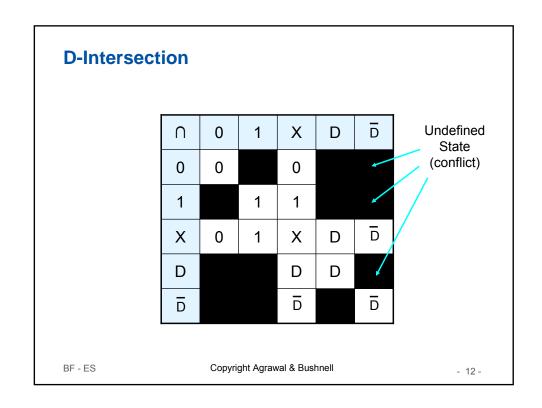

#### **Definition: D-Cubes**

- D-cubes are singular covers with five-valued signals

- Used for D-drive (propagation of D through gates) and forward implication.

Examples:

$XDX \cap 1D\overline{D} = 1D\overline{D}$   $0DX \cap 0D1 = 0D1$  $D\overline{D}X \cap D\overline{D}1 = D\overline{D}1$

| D-cube | а  | b  | С  |

|--------|----|----|----|

| D-1    | D  | 1  | O  |

| D-2    | 1  | D  | D  |

| D-3    | D  | 1  | D  |

| D-4    | 1  | םו | D  |

| D-5    | D  | D  | ΟI |

| D-6    | םו | םו | D  |

| D-7    | D  | 0  | 1  |

| D-8    | 0  | D  | 1  |

| D-9    | D  | סו | 1  |

| D-10   | םו | D  | 1  |

BF - ES

Copyright Agrawal & Bushnell

- 13 -

# **Complexity of D-Algorithm**

- Signal values on all lines (PIs and internal lines) are manipulated using 5-valued algebra.

- Worst-case combinations of signals that may be tried is 5<sup>#lines</sup>

- For XOR circuit, 5<sup>12</sup> = 244,140,625.

- Podem: A reduced-complexity ATPG algorithm

- · Recognizes that internal signals depend on Pls.

- Only PIs are independent variables and should be manipulated.

- Because faults are internal, a PI can assume only 3 values (0, 1, X).

- Worst-case combinations = 3<sup>#PI</sup>; for XOR circuit, 3<sup>2</sup> = 8.

BF - ES - 16 -

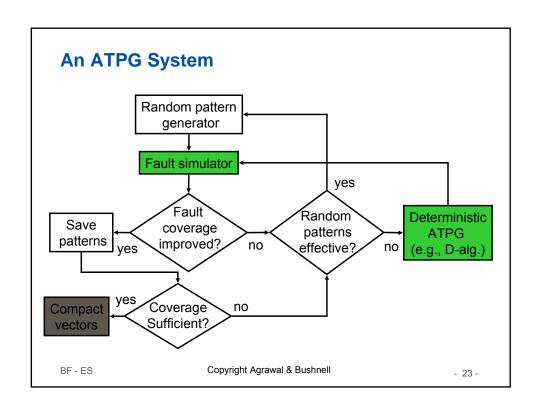

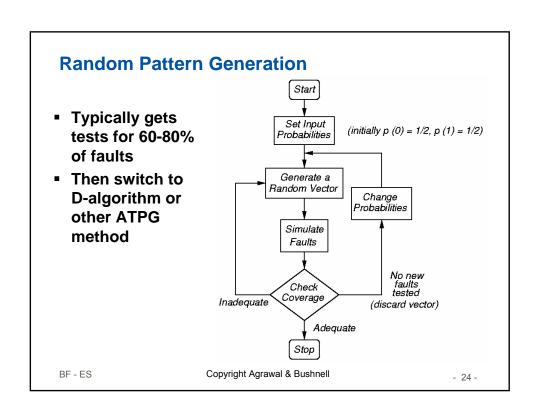

### **Fault coverage**

A certain set of test patterns will not always detect all faults that are possible within a fault model

$coverage = \frac{\text{Number of detectable faults for a given test pattern set}}{\text{Number of faults possible due to the fault model}}$

For actual designs, the coverage should be at least in the order of 98 to 99%

BF - ES - 17 -

#### **Fault simulation**

- Coverage can be computed with fault simulation:

- ∀ faults ∈ fault model: check if distinction between faulty and the fault-free case can be made:

```

Simulate fault-free system;

∀ faults ∈ fault model DO

∀ test patterns DO

Simulate faulty system;

Can the fault be observed for ≥1 pattern?

Faults are called redundant if they do not affect the observable behavior of the system,

```

Fault simulation checks whether mechanisms for improving fault tolerance actually help.

BF - ES - 18 -

# **Finding Other Detected Faults by the Generated Test**

- Determine good circuit signal values.

- For each fault

- Place a D or  $\overline{D}$  at the fault site

- · Perform forward implications

- Fault is detected if any PO assumes a D or  $\overline{D}$  value

BF - ES - 19 -

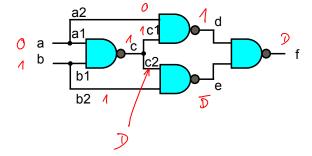

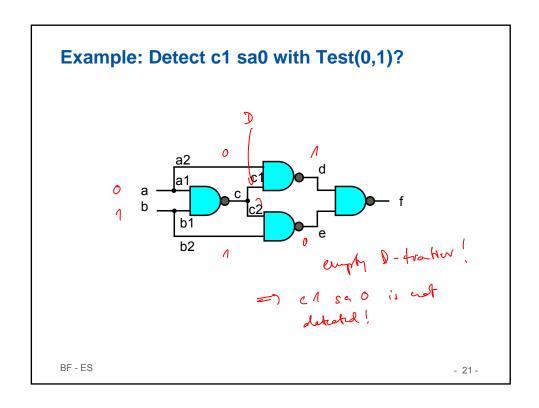

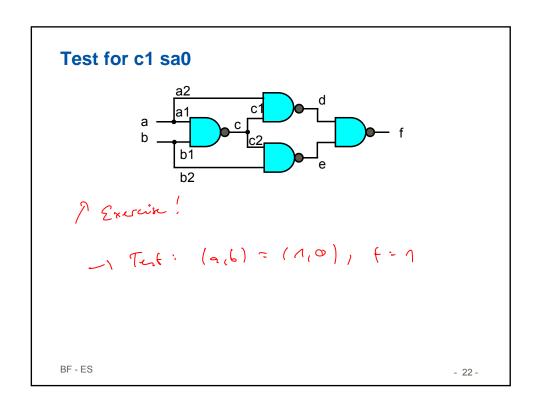

# Example: Detect c2 sa0 with Test(0,1)?

BF - ES - 20 -

### **Vector Compaction**

- Objective: Reduce the size of test vector set without reducing fault coverage.

- Simulate faults with test vectors in reverse order of generation

- ATPG patterns go first

- Randomly-generated patterns go last (because they may have less coverage)

- When coverage reaches 100% (or the original maximum value), drop remaining patterns

- Significantly shortens test sequence ⇒ testing cost reduction.

BF - ES Copyright Agrawal & Bushnell - 25 -

# **Static and Dynamic Compaction of Sequences**

- Static compaction

- · ATPG should leave unassigned inputs as X

- Two patterns compatible if no conflicting values for any PI

- Combine two tests  $t_a$  and  $t_b$  into one test  $t_{ab}$  =  $t_a \cap t_b$  using intersection

- Detects union of faults detected by  $t_a$  and  $t_b$

- Dynamic compaction

- · Process every partially-done ATPG vector immediately

- · Assign 0 or 1 to PIs to test additional faults

BF - ES Copyright Agrawal & Bushnell - 26 -

# Example

$$t_1 = 0.1 \text{ X}$$

$t_2 = 0 \text{ X} 1$

$t_3 = 0 \text{ X} 0$   $t_4 = \text{ X} 0.1$

$$t_2 = 0 \times 1$$

$$t_3 = 0 \times 0$$

$$t_4 = X \ 0 \ 1$$

BF - ES

- 27 -

# **Design for testability**

BF - ES

- 28 -

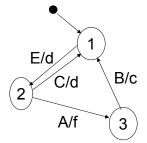

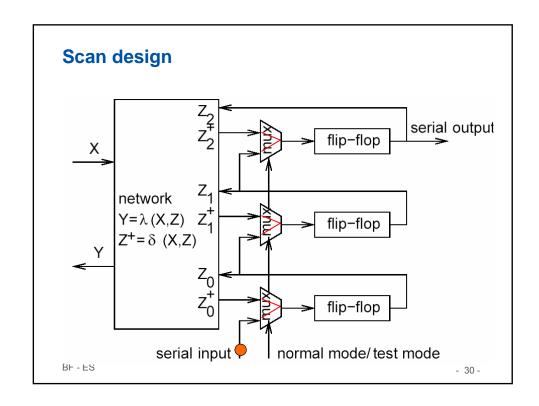

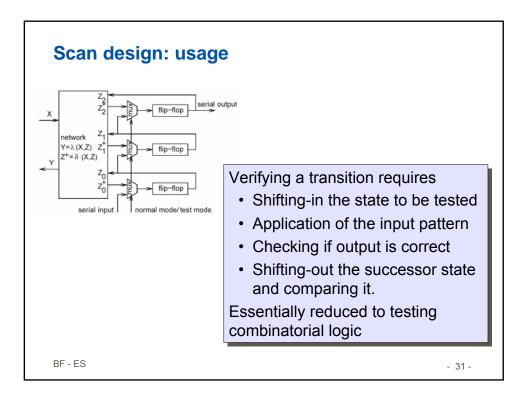

# **Testing finite state machines**

Difficult to check states and transitions.

For example, verifying the transition from state 2 to 3 requires

- Getting into state 2

- Application of A

- Check if output is f

- Check if we have actually reached 3

Can be simplified by "design for testability"

→ Scan design

BF - ES

- 29 -

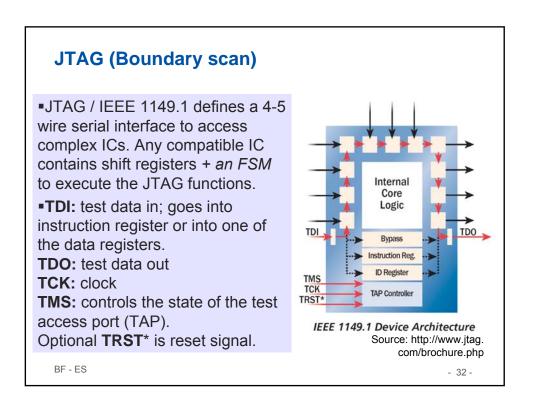

### Limitations of a single serial scan chain

- For chips with a large number of flip-flops, serial shifts can take a quite long time.

- Hence, it becomes necessary to provide several scan chains.

- Trying to avoid serial shifts by generating test patterns internally and by also storing the results internally.

- Compaction of circuit response in a signature. Shifting the entire result out becomes obsolete, we just shift out the signature.

BF - ES - 33 -

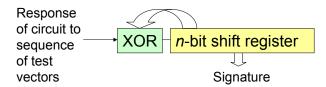

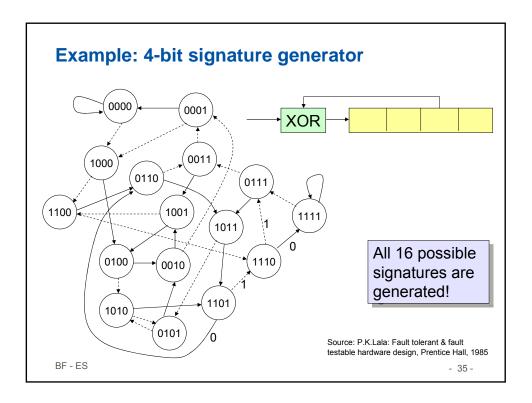

# Signature analysis

- Response of circuit to sequence of test patterns compacted in a signature. Only this signature is compared to the golden reference.

- In order to exploit an n-bit signature register as good as possible, we try to use all possible values.

- In practice, we use shift-registers with linear feedback:

Using proper feedback bits, all possible values for the register can be generated.

BF - ES - 34 -

# **Aliasing for signatures**

#### Consider aliasing for some current pattern

- An *n*-bit signature generator can generate 2<sup>n</sup> signatures.

- For an m-bit input sequence, the best that we can get is to evenly map  $2^{(m-n)}$  patterns to the same signature.

- Hence, there are  $2^{(m-n)}$ -1 sequences that map to the same signature as the pattern currently considered.

- In total, there are  $2^m$ -1 sequences different from the current one.

$$P = \text{Probability} \left( \frac{\text{other patterns map to same signature}}{\text{total number of other patterns}} \right) = \frac{2^{(m-n)} - 1}{2^m - 1}$$

$P = \frac{1}{2^n}$  for m >> n provided that we evenly map patterns to signatures

BF - ES - 36 -

18

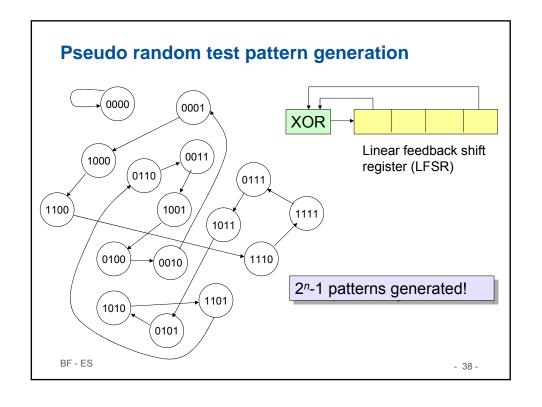

### Replacing serially shifted test pattern by pseudo-random test patterns Shifting in test patterns can be avoided if we generate (more or less) all possible test patterns internally with a pseudorandom test pattern generator. Pseudo-DUT Signature Compare analysis random with test pattern register reference generator •Effect of pseudo random numbers on coverage to be analyzed. •Signature analysis register shifted-out at the end of the test. Comparison possible because test pattern generator is a deterministic source! BF - ES

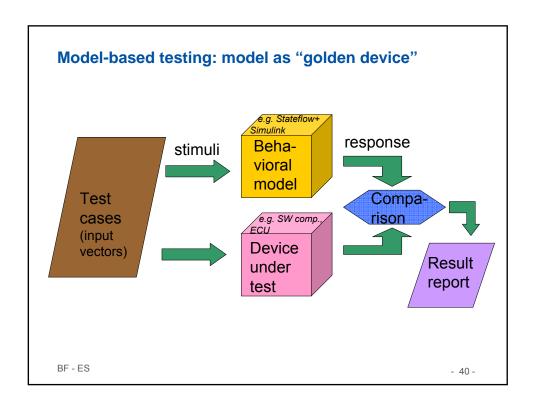

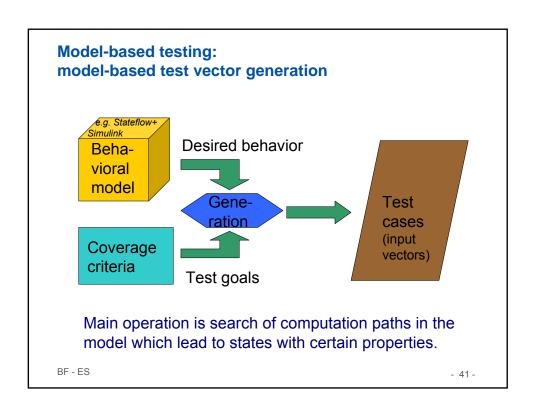

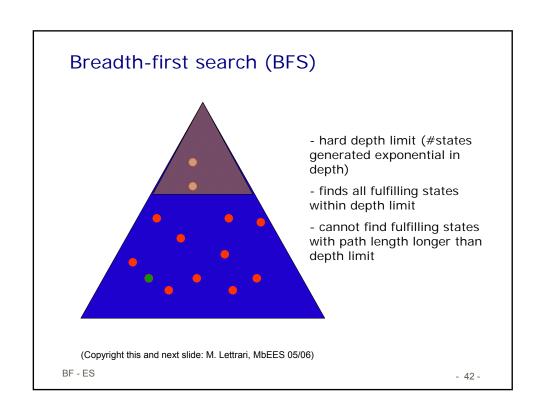

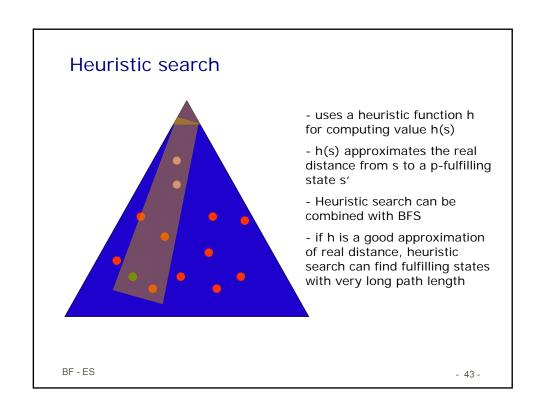

# Model-based testing BF-ES - 39-

# Fault Injection BF-ES

### **Fault injection**

- Fault simulation may be too time-consuming

- If real systems are available, faults can be injected.

- Two types of fault injection:

- 1. local faults within the system, and

- faults in the environment (behaviors which do not correspond to the specification).

For example, we can check how the system behaves if it is operated outside the specified temperature or radiation ranges.

BF - ES - 45 -

# **Fault injection**

- Intentional activation of faults by HW or/and SW means

- Establish faults in a predictable and reproducible way

- Trigger error-handling routines

- Two purposes:

- Testing and Debugging

- During normal operation faults are rare events

- May be much too rare to achieve meaningful data from std. testing

- Dependability Forecasting

- Used for deriving data about the likely dependability of the system

- Need to know the types and frequencies of different faults in the intended operational environment

BF - ES - 46 -

# **Software Fault Injection**

- Errors are seeded into memory by software

- Mimic errors originating in hardware faults by software

- Either randomly or in specific location to provoke specific faultmanagement routine

- Advantages over physical fault injection include

- Predictability and reproducibility: fault injection is independent of uncontrollable or statistical effects

- Reachability of inner registers in VLSI chips

- Simplicity of experiments: can be carried out with software tools

- Coverage similar to physical fault injection, if well-done

- Statistical data gathered from physical injection experiments can be used to trim software fault injection

BF - ES - 47 -

# Typical forms of SW fault injection

- Random bit flips in memory

- Simulates adverse operational conditions corrupting memory

- Boolean masking of words written to (some) memory

- Discard some message(s)

- · Simulates imperfect communication media

- Adding messages

- Simulates presence of a babbling idiot

- Checks consequences of certain fault tolerance mechanisms (resend...)

if used when transient fault condition was no longer present (very hard to

test by HW fault injection)

- Delaying messages / result delivery

- ...and many more

BF - ES - 48 -