# **Embedded Systems**

$\mathbf{N}$

#### Thursday

- Midterm exam: December 16th, 2010, AudiMO, 16:00 - 19:00

- No lecture on December 16th

- Open book: bring any handwritten or printed notes, or any books you like.

- Please bring your ID.

# **Exam Policy**

Midterm/End-of-Term Exam/End-of-Semester Exam

# Requirement for admission to end-of-term and end-of-semester exams:

- > 50% of points in problem sets,

- > 50% of points in each project milestone, and

- > 50% of points in midterm exam

#### • Final grade:

best grade in end-of-term or end-of-semester exam

#### Example

#### **REVIEW**

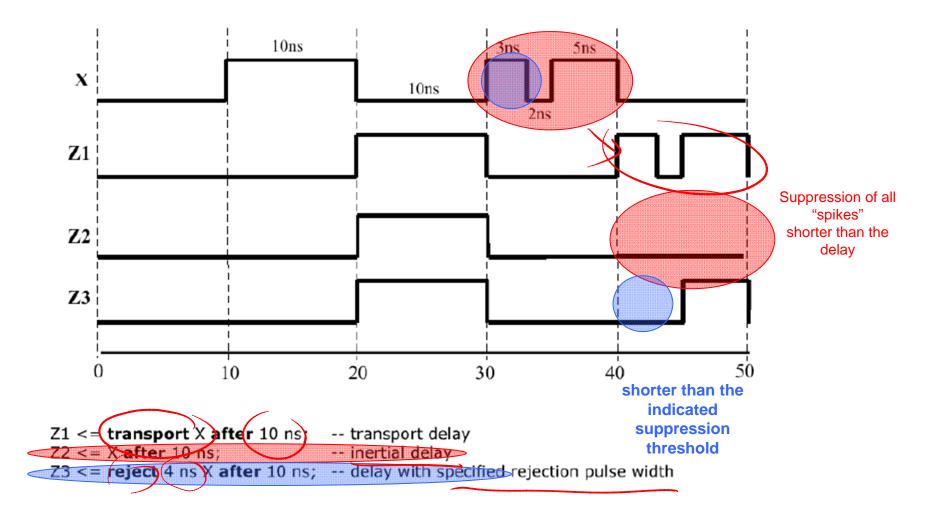

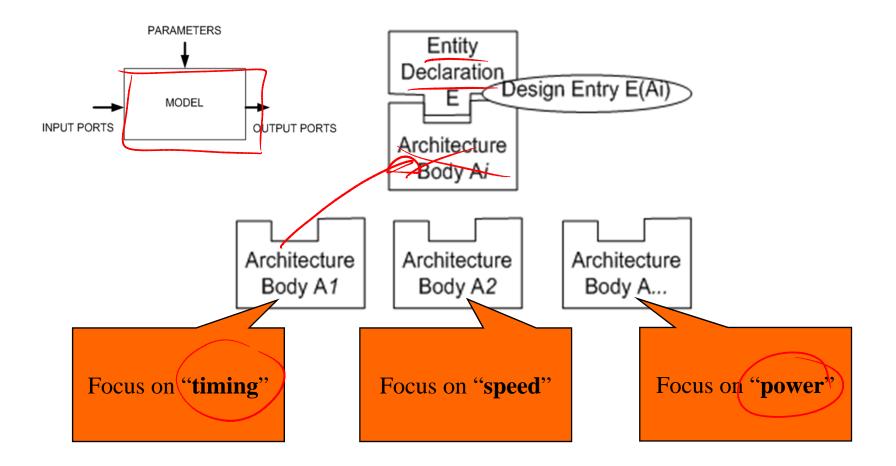

#### **Modeling Behavior**

- Architecture body

- describes an implementation of an entity

- may be several per entity

- Behavioral architecture

- describes the algorithm performed by the module

- contains

- process statements, each containing

- sequential statements, including

- signal assignment statements and

- wait statements

#### **REVIEW**

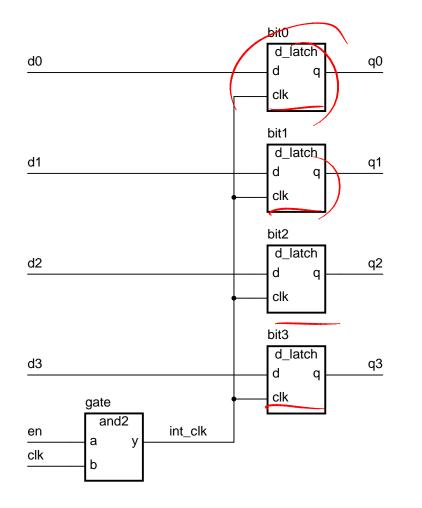

#### **Modeling Structure**

- *Structural* architecture

- implements the module as a composition of subsystems

- contains

- signal declarations, for internal interconnections

- the entity ports are also treated as signals

- component instances

- instances of previously declared entity/architecture pairs

- port maps in component instances

- connect signals to component ports

- wait statements

#### **REVIEW**

#### **Structure Example**

architecture struct of reg4 is **signal** int\_clk : bit; begin bit0 : entity work.d\_latch(basic) port map ( d0, int\_clk, q0 ); bit1 : entity work.d\_latch(basic) port map ( d1, int\_clk, q1 ); bit2 : entity work.d\_latch(basic) port map ( d2, int\_clk, q2 ); bit3 : **entity** work.d\_latch(basic) port map ( d3, int\_clk, q3 ); gate : **entity** work.and2(basic) port map ( en, clk, int\_clk ); end architecture struct;

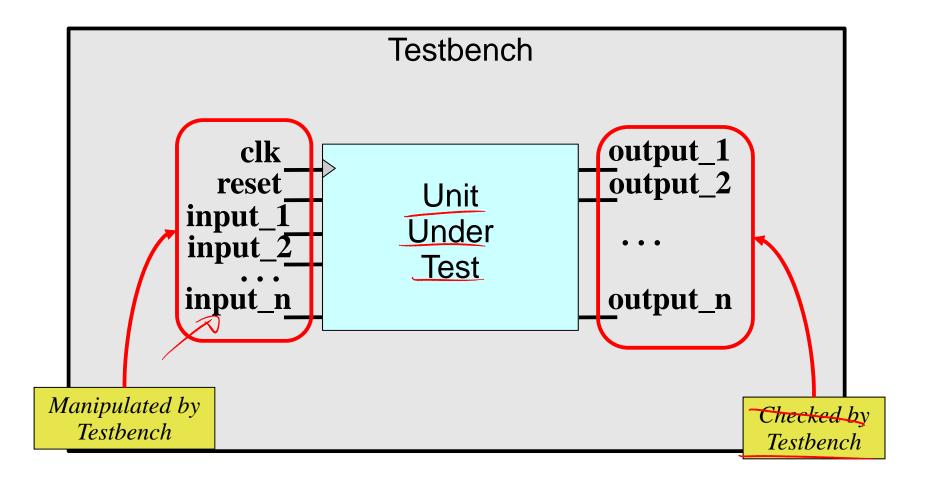

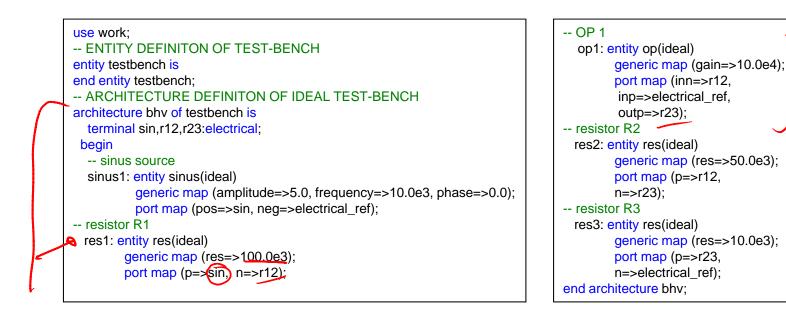

#### **Testbench Structure**

#### **File Input**

- Using assert to check behaviour implies writing correct behaviour twice

- Instead, write expected behaviour in file:

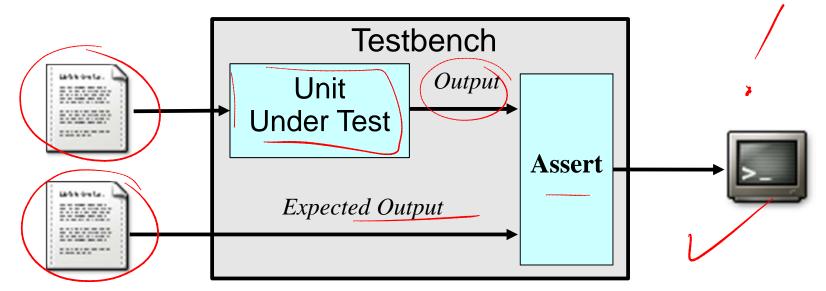

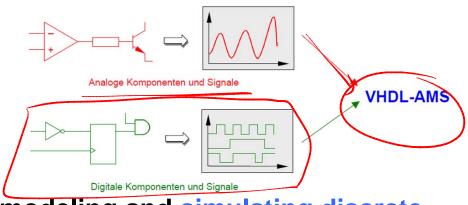

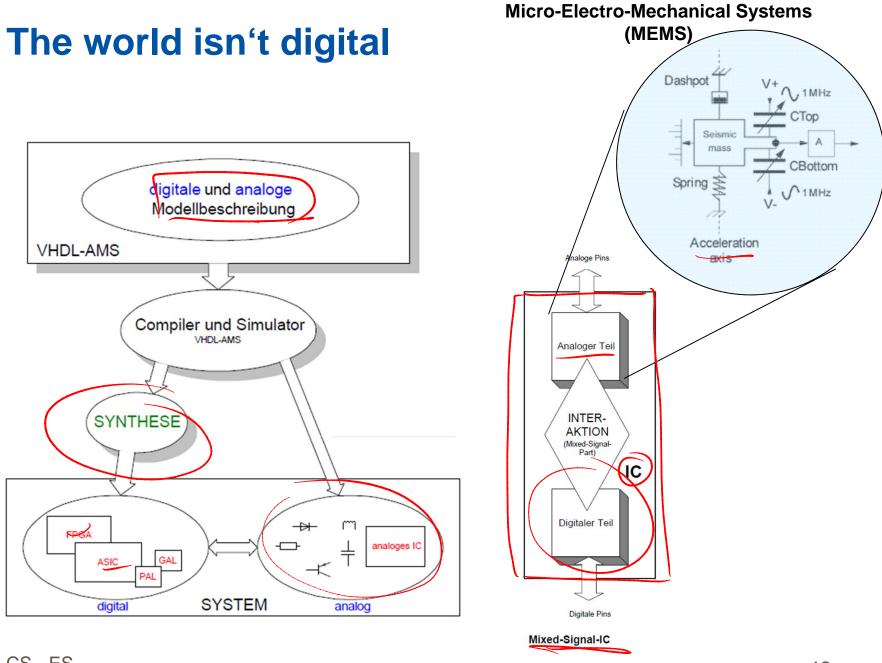

# Introduction to VHDL-AMS

# Introduction

- VHDL 1076 is suitable for modeling and simulating discrete systems

- Many of today's designs include at least some continuous characteristics:

- System design

- Mixed-signal electrical designs

- Mixed electrical/non-electrical designs

- Analog design

- Analog behavioral modeling and simulation

- Digital design

- Detailed modeling (e.g. submicron effects)

- Designers want a uniform description language

CS - ES

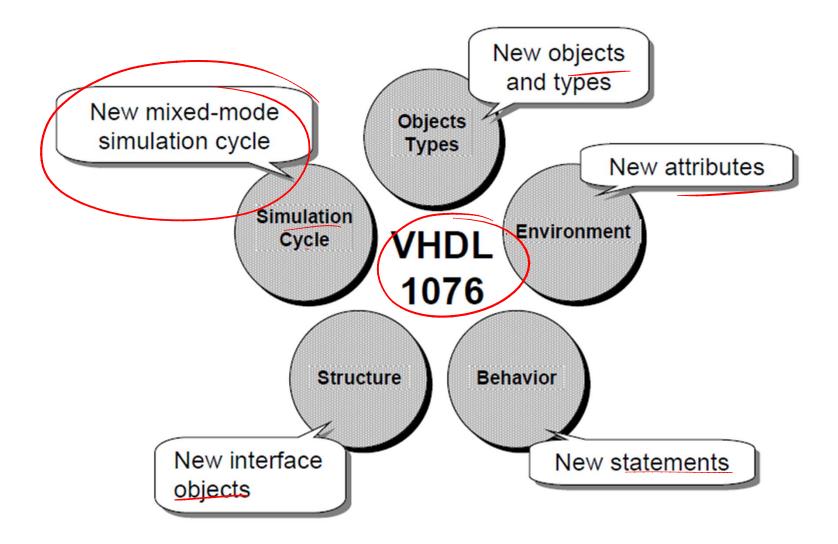

#### **VHDL-AMS Language Architecture**

# **VHDL-AMS Highlights (1)**

- Superset of VHDL 1076

- Full VHDL 1076 syntax and semantics is supported

- Adds new simulation model supporting continuous behavior

- Continuous models based on differential algebraic equations (DAEs)

- DAEs solved by dedicated simulation kernel: the analog solver

- Handling of initial conditions, piecewise-defined behavior, and discontinuities

6.71

# **VHDL-AMS Highlights (2)**

- Extended structural semantics

- Conservative semantics to model physical systems

- e.g. Kirchhoff's laws for electrical circuits

- Non-conservative semantics for abstract models

- Signal-flow descriptions

- Mixed-signal interfaces

- Models can have digital and analog ports

- Mixed-signal semantics

- Unified model of time for a consistent synchronization of

- mixed event-driven/continuous behavior

- Mixed-signal initialization and simulation cycle

- Mixed-signal descriptions of behavior

- Frequency domain support

- Small-signal frequency and noise modeling and simulation

#### **Multiple Architectures per Entity**

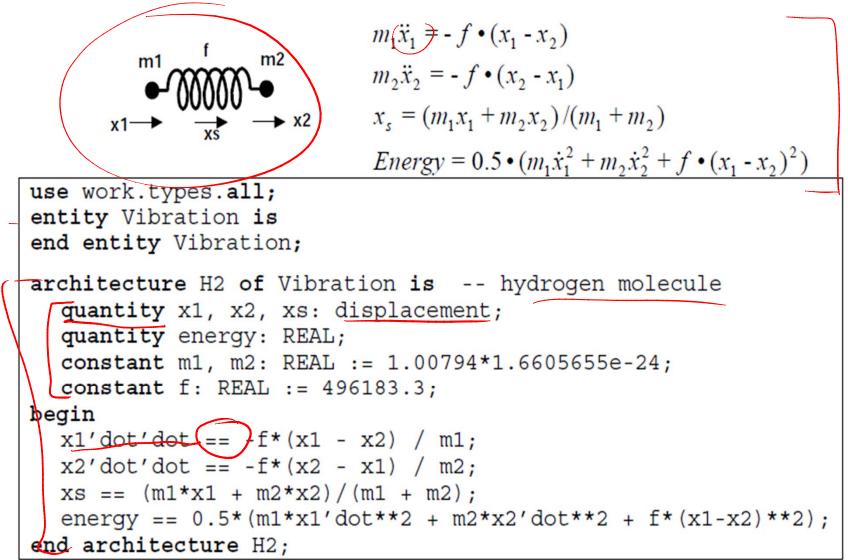

# First approximation: one-dimensional spring model

- New object in VHDL 1076.1

- Represents an unknown in the set of differential algebraic equations implied by the text of a model

- Continuous-time waveform

- Scalar subelements must be of a floating-point type

- Default initial value for scalar subelements is 0.0

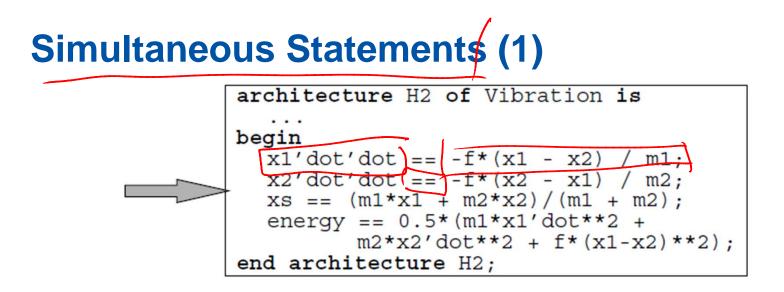

- New class of statements in VHDL 1076.1

- Simple simultaneous statements express relationships between quantities

- Left-hand side and right-hand side must be expressions with scalar subelements of a floating point type

- Statement is symmetrical w.r.t. its left-hand and right-hand sides

- Expressions may involve quantities, constants, literals, signals, and (possibly user-defined) functions

- At least one quantity must appear in a simultaneous statement

# **Simultaneous Statements (2)**

- Analog solver is responsible for computing the values of the quantities such that the relationships hold (subject to tolerances)

- Simultaneous statements may appear anywhere a concurrent statements may appear

- The order of simultaneous statements does not matter

- Other forms for simultaneous statements:

- Simultaneous if statement

- Simultaneous case statement

- Simultaneous procedural statement

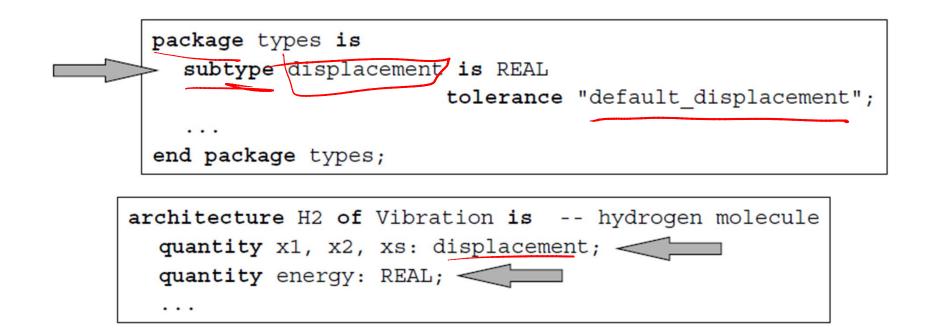

# **Tolerances (1)**

- Numerical algorithms used by analog solver can only find an approximation of the exact solution

- Tolerances are used to specify how good the solution must be

- Each quantity and each simultaneous statement belongs to a tolerance group indicated by a string expression

- All members of a tolerance group have the same tolerance characteristics

- The language does not define how a tool uses tolerance group

# **Tolerances (2)**

A quantity gets its tolerance group from its subtype

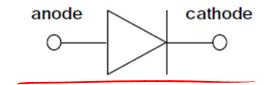

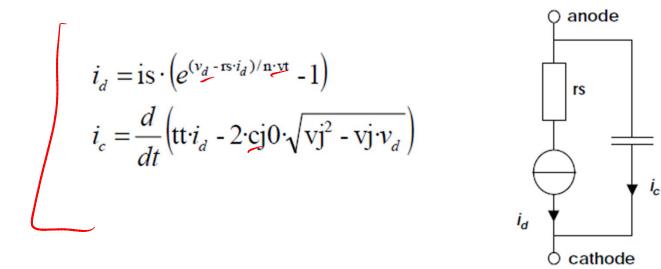

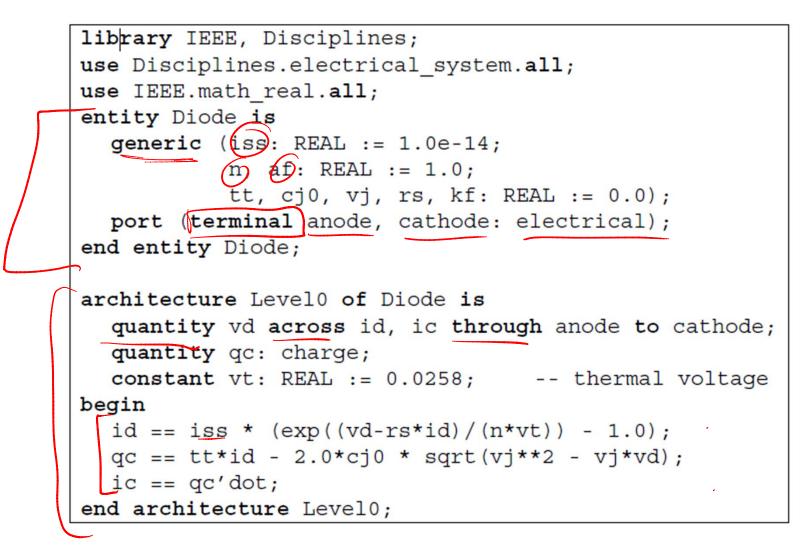

#### **Parameterized Diode**

Example of a conservative model of an electrical component

Simple large-signal model

#### **VHDL-AMS Model of Diode**

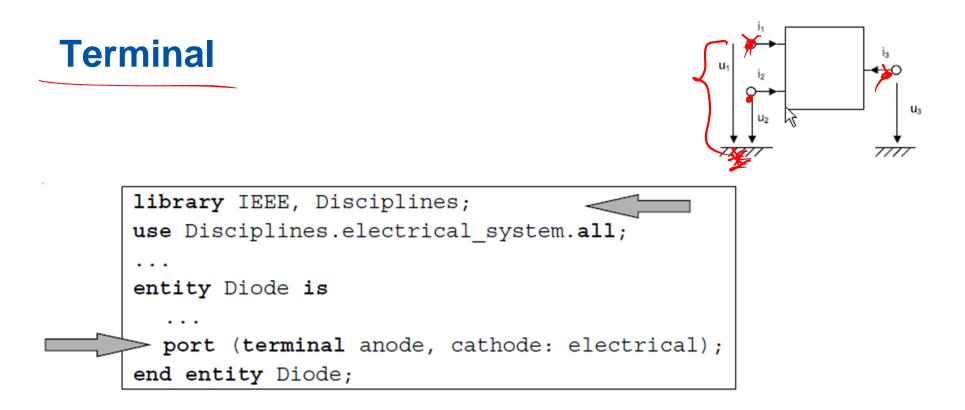

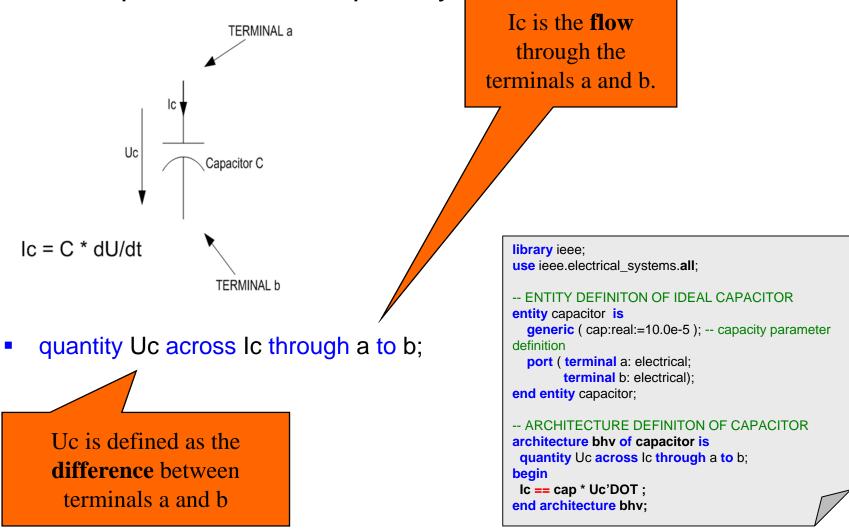

- New object in VHDL 1076.1

- Basic support for structural composition with conservative semantics

- Belongs to a nature

- Nature electrical defined in package electrical\_system

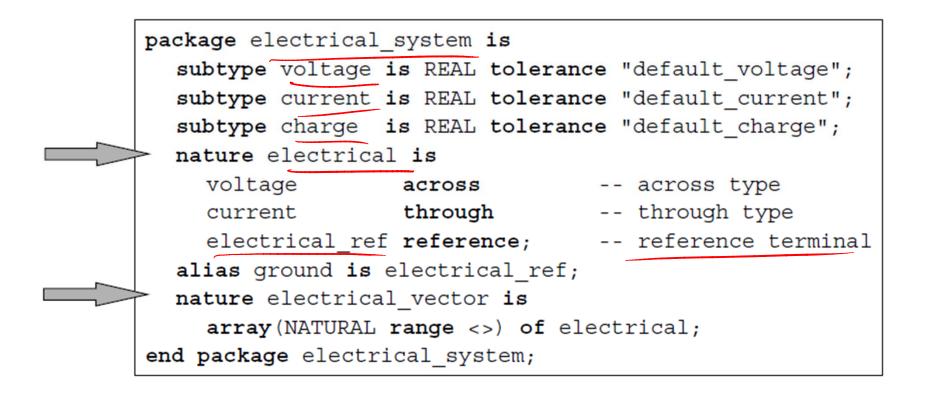

#### Nature

- Represents a physical discipline or energy domain

- Electrical and non-electrical disciplines

- Has two aspects related to physical effects

- Across: effort like effects (voltage, velocity, temperature, etc.)

- Through: flow like effects (current, force, heat flow rate, etc.)

- A nature defines the types of the across and through quantities incident to a terminal of the nature

- A scalar nature additionally defines the reference terminal for all terminals whose scalar subelements belong to the scalar nature

- A nature can be <u>composite</u>: array or record

- All scalar subelements must have the same scalar nature

- No predefined natures in VHDL 1076.1

#### **Electrical Systems Environment**

Assume package is compiled into a library Disciplines

#### **NATURES**

Physical disciplines or energy domains

VHDL-AMS not limited to electrical quantities

| Nature           | Effort           | Flow             |

|------------------|------------------|------------------|

| electrical       | voltage          | current          |

| thermal          | temperature      | heat flow rate   |

| kinematic_v      | velocity         | force            |

| rotational_omega | angular velocity | torque           |

| fluidic          | pressure         | volume flow rate |

| nature electrical is                                 |                                              |  |

|------------------------------------------------------|----------------------------------------------|--|

| voltage across                                       | <ul> <li>across type is 'voltage'</li> </ul> |  |

| current through                                      | through type is 'current'                    |  |

| electrical_ground reference; reference terminal name |                                              |  |

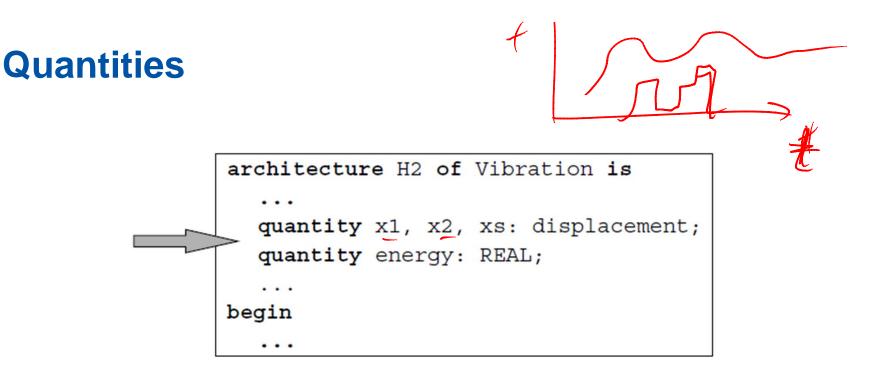

#### **Quantities**

- For analog modeling

- Continuous time or frequency waveforms

- Quantities:

- Free Quantities (for signal flow modeling)

- Branch Quantities (for modeling of conservative energy systems)

- Source Quantities (for frequency and noise modeling)

**Syntax:** quantity\_name {,...}: subtype\_indication [:= expression];

#### **Free Quantity**

- To break down complex equations into manageable pieces or for data flow description

- Auxiliary variable

- Quantity name(s), double subtype and optionally an initial value expression

quantity Vint : real := 5.0 ;

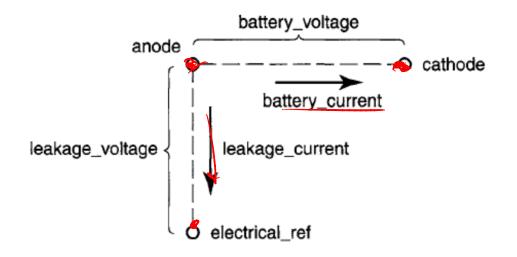

## **Branch Quantity**

- Branch between two terminals

- Constraints between branches that share terminal (Kirchhoff's laws in electrical domain)

- Branch quantities are used by equations of models

terminal anode, cathode: electrical; quantity battery\_voltage <u>across</u> battery\_current through anode to cathode; quantity leakage\_voltage across battery\_current through anode;

# **Branch Quantity**

Example of a branch quantity

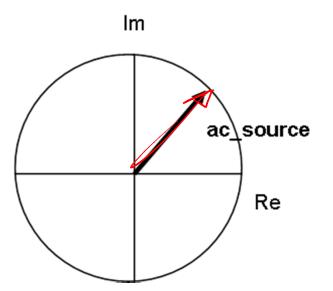

- Specification of energy sources in frequency domain

- E.g. voltage source

quantity ac\_source: real spectrum 1.0, 45.0;

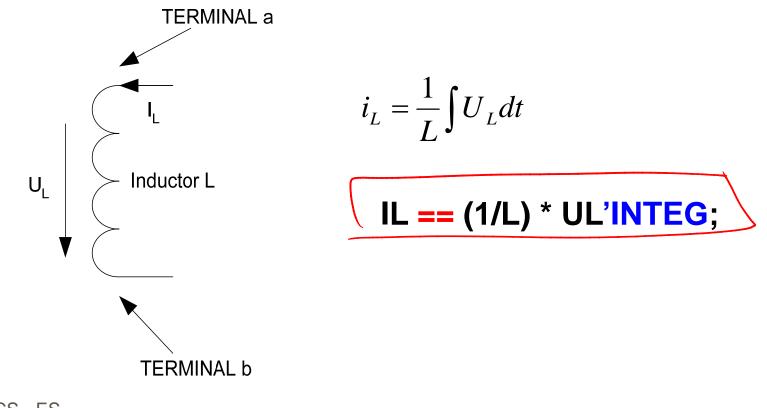

#### **Quantity Attributes**

- quantity\_name'DOT

- quantity\_name'INTEG

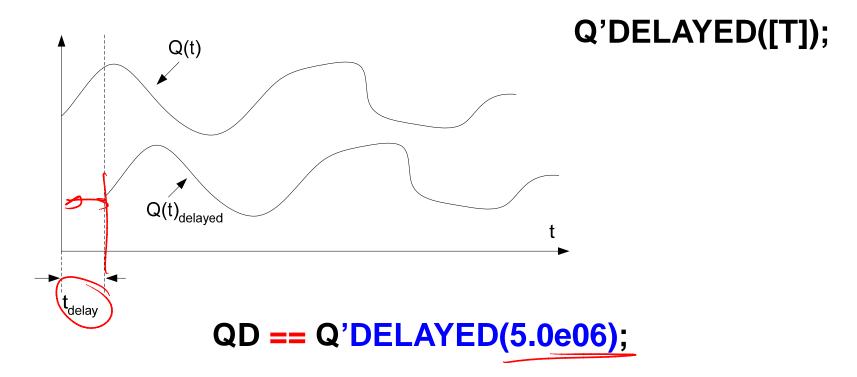

- quantity\_name'DELAYED[(T)]

- quantity\_name'SLEW[(maxrise)[,(maxfall])]

- quantity\_name'LTF(num,den)

- quantity\_name'ZOH(TSampl[,(init\_delay])

- quantity\_name'ZTF(num,den,t[,init\_del])

- quantity\_name'ABOVE(level)

Differential algebraic equation (DAE)

SLEW (RISE, FALL) Laplace Transfer Function

Z-Domain transfer function

- Integral function

- Needs to be initialized at zero time

#### **Q'DELAYED**

Delay of quantity for specific time unit

## **Q'LTF**

- Laplace Transfer Function

- num, den static expressions of type real\_vector

$$H(s) = \frac{\sum a_{k} s^{k}}{\sum b_{k} s^{k}}$$

Q'LTF(num, den);

constant num : real\_vector := (1.0, 2.0, 1.0); constant den : real\_vector := (1.0, 0.0, -1.0);

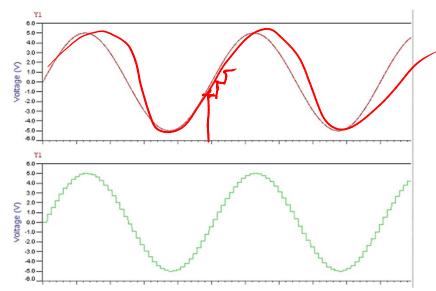

## Sample-and-Hold function

A/D D/A Converters

#### Q'ZOH(Tsampl [init\_delay]);

NOTE: Controlled assignment of discrete value of quantity to signal type variable -> S <= Q'ZOH(t\_sampl);</li>

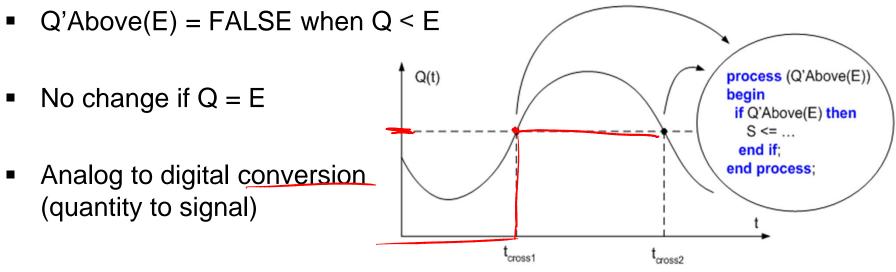

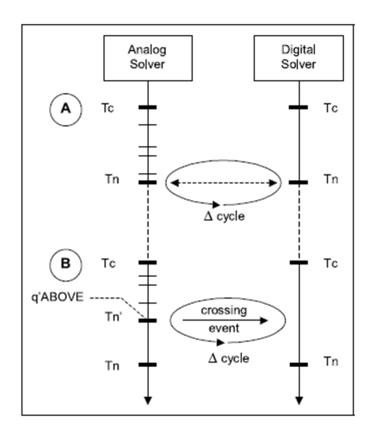

#### **Q'ABOVE**

- Quantity boolean signal

- Q'Above(E) = TRUE when Q > E

Used to trigger processes

#### **Q'Above – An example**

#### • 1 bit ADC

**library** IEEE; **use** IEEE.electrical\_systems.all;

entity adc is generic (Vref: real := 5.0) -- ref voltage port (terminal inp : electrical; -- input signal outp: out bit); -- output end entity adc; architecture one of adc is quantity Vin across inp to ref; -- input voltage begin

p1: process (Vin'above(Vref))

begin

if (Vin'above(Vref)) then

outp <= '1':

else

outp <= '0';

end if;

end process p1;

end architecture one ;</pre>

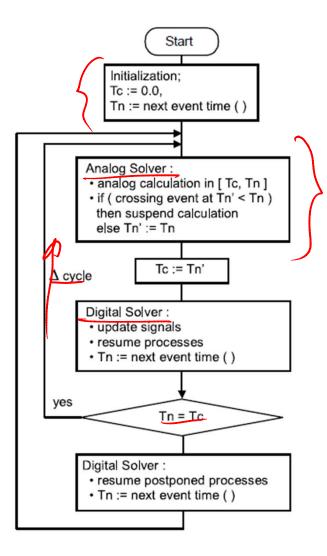

#### **Time Domain Simulation Cycle**

Tc – current time Tn – next time

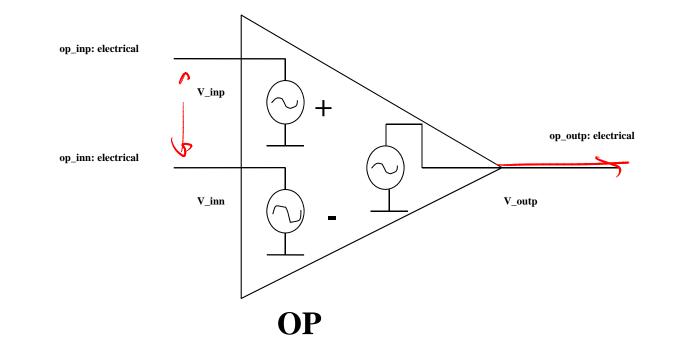

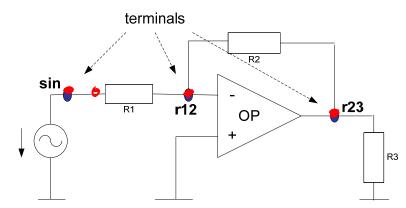

#### IDEAL OP amplifier

$$V\_out = Gain \bullet (V\_inp - V\_inn)$$

CS - ES

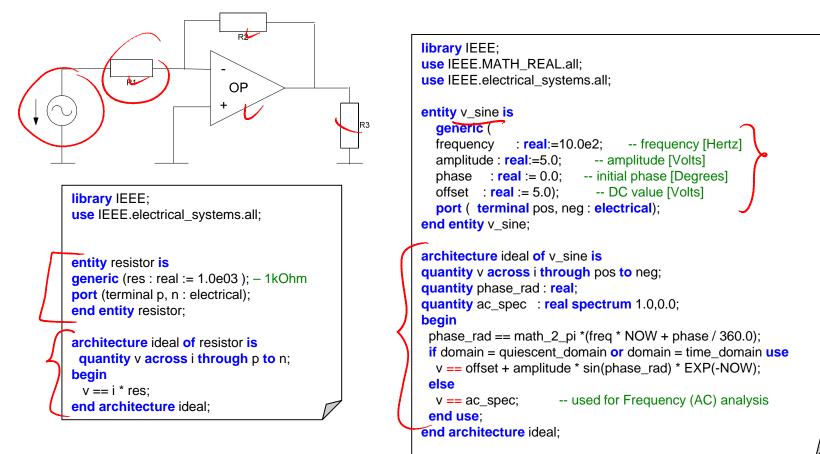

#### Declaration of OP entity

library ieee; use ieee.electrical\_systems.all;

```

-- ENTITY DEFINITON OF IDEAL OP AMPLIFIER

entity op is

generic (gain:real:=10.0e5); -- gain parameter definition

port (terminal op_inp: electrical; --

terminal op_inn: electrical; --

terminal op_outp: electrical);--

end entity op;

```

Declaration of OP architecture (operational)

-- ARCHITECTURE DEFINITON OF IDEAL OP architecture ideal of op is quantity v\_inp across op\_inp to electrical\_ref; quantity v\_inn across op\_inn to electrical\_ref; quantity v\_outp across i\_outp through op\_outp to electrical\_ref; begin V\_outp == gain \* (v\_inp - v\_inn); -- simultaneous statement end architecture ideal;

Models for resistor and voltage source

- 45 -

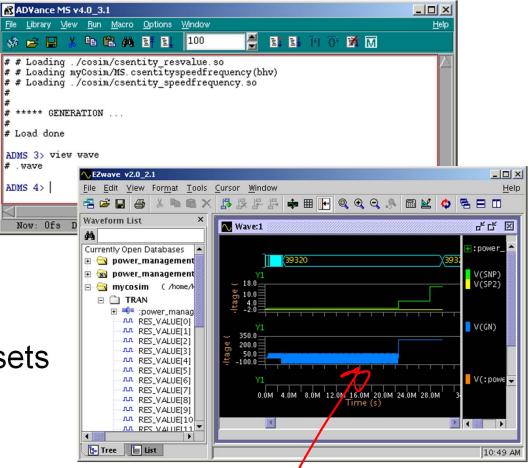

## **VHDL-AMS EDA Tools**

- MentorGraphics

- ADVanceMS

- SystemVision

- Cadence

- SimVision

- Support different subsets of the language

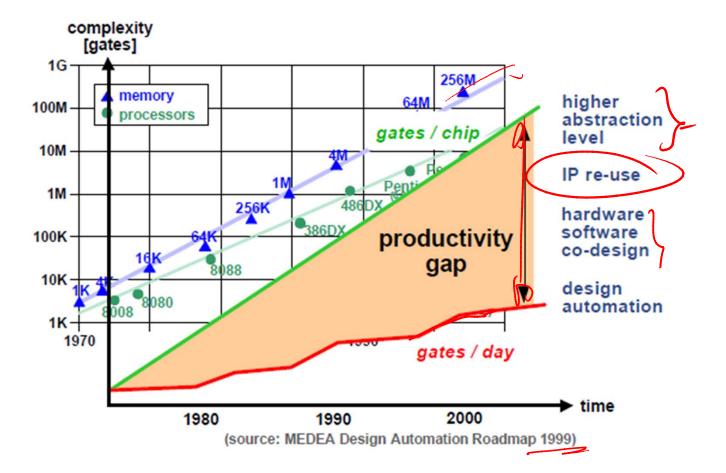

#### **Productivity Gap**

## Introduction

The followings are not supported by native C/C++

- Hardware style communication

- Signals, protocols, etc.

- Notion of time

- Cycle/clock, delay, time sequenced op., etc.

- Concurrency

- HW operates in parallel.

- Reactivity

- HW responds to stimuli.

- Hardware data types

- Bits, bit-vector types, multi-valued logic type, and so on.

SystemC is modeling platform consisting of a set of <u>C++ class library</u>, plus a simulation kernel that supports hardware modeling concepts at the system level, behavioral level and register transfer level.

### **SystemC features**

- Processes

- Clocks

- Hardware data types

- Waiting and watching

- Modules, ports, and signals

- Channel, interface, and event

- $\rightarrow$  for concurrency

- $\rightarrow$  for time

- $\rightarrow$  bit vectors, 4-valued logic, ....

- →for reactivity

- $\rightarrow$  for hierarchy

- $\rightarrow$  abstract communications

- Simulation support

- Support of multiple abstraction levels and iterative refinement

## SystemC V2.0 language structure

Upper layers are built cleanly on lower layers.

Lower layers can be used without upper layers.

| Standard Channel<br>Various MOCs<br>Kahn Process Netw<br>Static Dataflow, e        | Master/Slave Library<br>etc.                                                                                                                                                                              |  |  |  |  |  |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Elementary Channels<br>Signal, Timer, Mutex, Semaphore, Fifo, etc.                 |                                                                                                                                                                                                           |  |  |  |  |  |

| Core Language<br>Modules<br>Ports<br>Processes<br>Interfaces<br>Channels<br>Events | Data Types<br>Logic Type (01XZ)<br>Logic Vectors<br>Bits and Bit Vectors<br>Arbitrary Precision Integers<br>Fixed Point Numbers<br>C++ Built-In Types (int, char, double, etc.)<br>C++ User-Defined Types |  |  |  |  |  |

| C++ Language Standard                                                              |                                                                                                                                                                                                           |  |  |  |  |  |

#### **Comparison: SystemC - VHDL**

|   |               | VHDL          | SystemC                   |

|---|---------------|---------------|---------------------------|

| > | Hierarchy     | entity        | module                    |

| A | Connection    | port          | port                      |

| > | Communication | signal        | signal                    |

| > | Functionality | process       | process                   |

| > | Test Bench    | Ŧ             | object orientation        |

| × | System Level  |               | channel, interface, event |

|   |               | $\frown$      | abstract data types       |

| > | I/O           | simple file ທ | C++ I/O capabilities      |

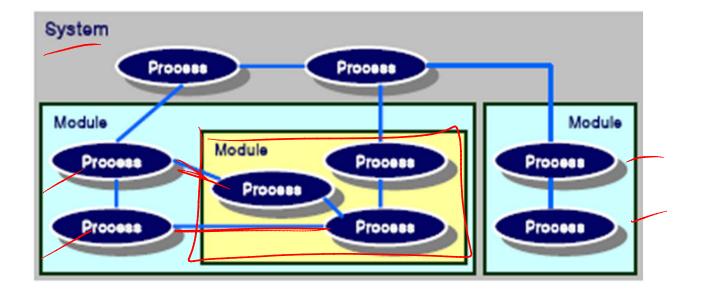

### SystemC system

- A system consists of a set of concurrent processes that describe functionality.

- Processes communicate with each other through channels.

- Processes can be combined into modules to create hierarchy.

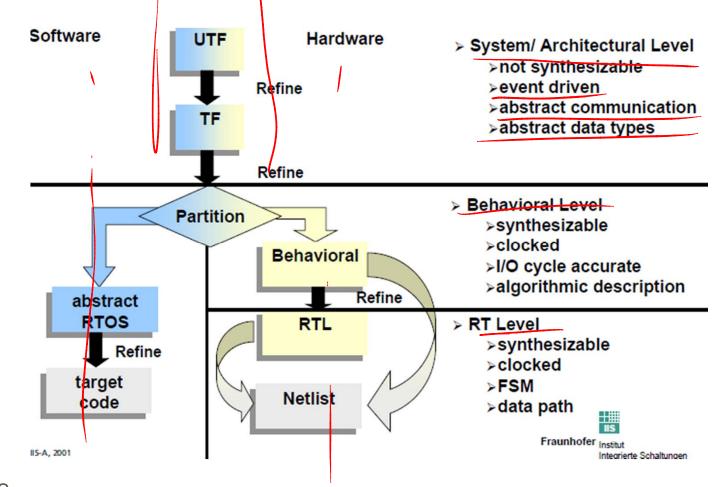

## SystemC design flow

Untimed functional (UTF)

A network of HW/SW neutral modules executing in zero times and communicating with abstract channels.

#### **Timed Functional (TF)**

A network of modules executing in some defined times and communicating with abstract channels. Allows allocation of time to behavioral blocks (using wait(delay))

CS - ES

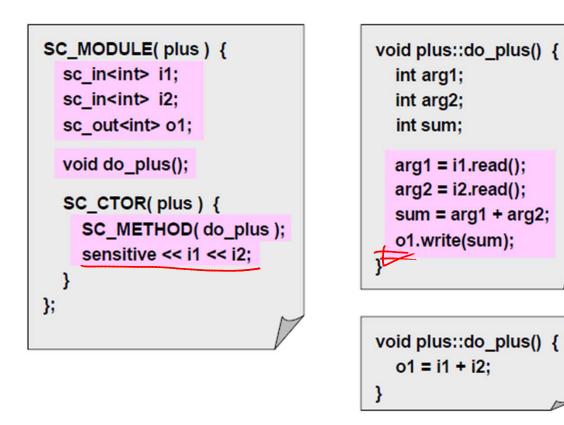

#### **Modules**

- Modules are basic building blocks of a SystemC design

- A module contains processes (→ functionality)

- and/or sub-modules (→hierarchical structure)

#### SC\_MODULE( module\_name ) {

**// Declaration of module ports**

**//** Declaration of module signals

// Declaration of processes

// Declaration of sub-modules

SC\_CTOR( *module\_name* ) { // Module constructor

// Specification of process type and sensitivity

**//** Sub-module instantiation and port mapping

```

}

```

// Initialization of module signals

};

CS - ES

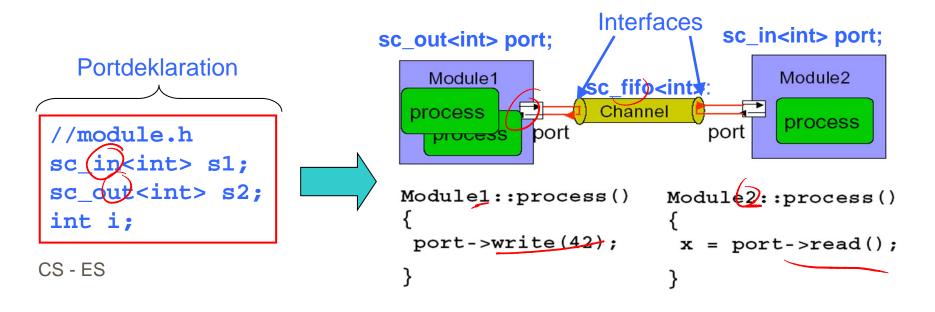

## Ports (1)

- Ports of a module are the external interfaces that pass information to and from a module

- In SystemC one port can be IN, OUT or INOUT

- Signals are used to connect module ports allowing modules to communicate

- Very similar to ports and signals in VHDL

#### **Ports and Signals**

- How to read and write a port ?

- Methods read(); and write();

- Examples:

- in\_tmp = in.read(); //reads the port in to in\_tmp

- out.write(out\_temp); //writes out\_temp in the out port

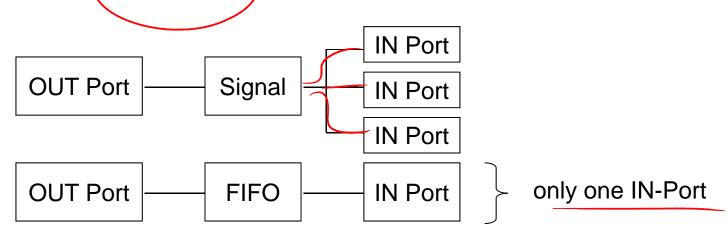

## **Signals**

- sc\_signal<T>

- Signal are also used for connecting two modules ports in parent module.

sc\_fifo<T>

- sc\_fifo is a predefined primitive channel intended to model the behavior of a fifo, that is, a first-in first-out buffer.

- sc\_buffer<T>

- like sc\_fifo (buffer size 1)

#### **Events**

- data type: sc\_event

- functionality:

- declaration: sc\_event my\_event;

- my\_event.notify(); // immediately

- my\_event.notify(SC\_ZERO\_TIME);// next delta Zyklus

- my\_event.notify(10, SC\_NS); // after 10 Ns

- waiting on event: wait( my\_event );

- process suspended until new event

#### Processes

- Process Semantics

- Encapsulates functionality

- Basic unit of concurrent execution

- Not hierarchical

- Process Activation

- Processes have sensitivity lists

- Processes are triggered by events on sensitive signals

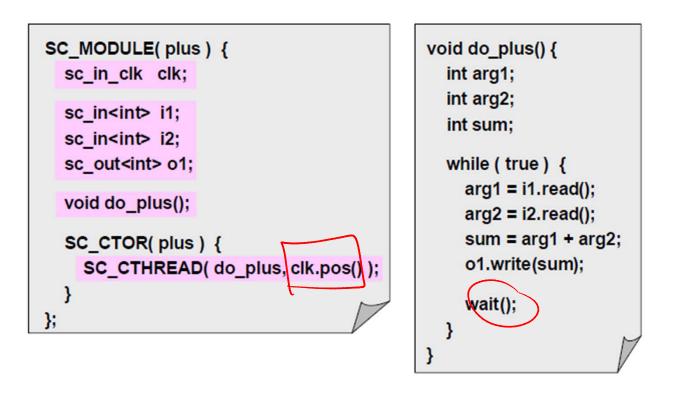

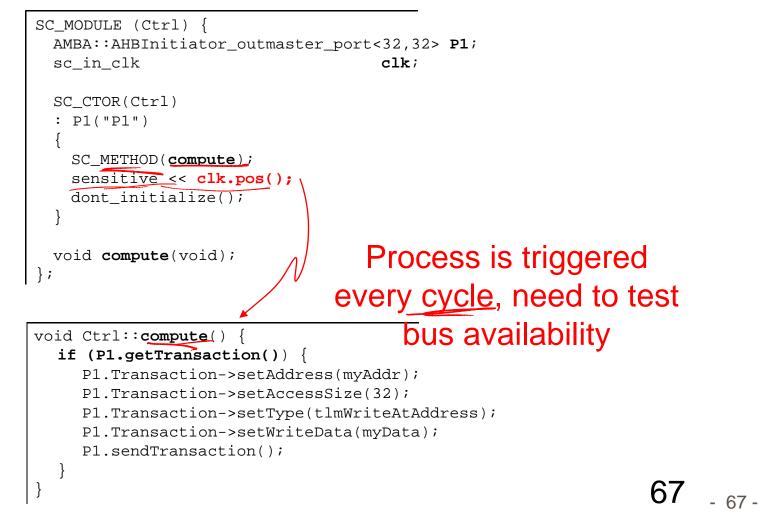

- Process Types

- Method (SC\_METHOD)

- asynchronous block, like a sequential function

- Thread (SC\_THREAD)

- asynchronous process

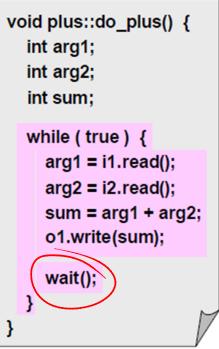

- Clocked Thread (SC\_CTHREAD)

- synchronous process

#### **Processes**

|                                       | SC_METHOD                                                                  | SC_THREAD                                                                  | SC_CTHREAD                                                       |

|---------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------|

| triggered                             | by signal events                                                           | by signal events                                                           | by clock edge                                                    |

| infinite<br>loop                      | no                                                                         | yes                                                                        | yes                                                              |

| execution suspend                     | no                                                                         | yes                                                                        | yes                                                              |

| suspend<br>& resume                   |                                                                            | wait()                                                                     | wait()<br>wait_until()                                           |

| construct<br>&<br>sentisize<br>method | <pre>SC_METHOD(p); sensitive(s); sensitive_pos(s); sensitive_neg(s);</pre> | <pre>SC_THREAD(p); sensitive(s); sensitive_pos(s); sensitive_neg(s);</pre> | SC_CTHREAD<br>(p,clock.pos());<br>SC_CTHREAD<br>(p,clock.neg()); |

| modeling<br>example<br>(hardware)     | combinational<br>logic                                                     | sequential logic<br>at RT level<br>(asynchronous<br>reset, etc.)           | sequential logic<br>at higher design<br>levels                   |

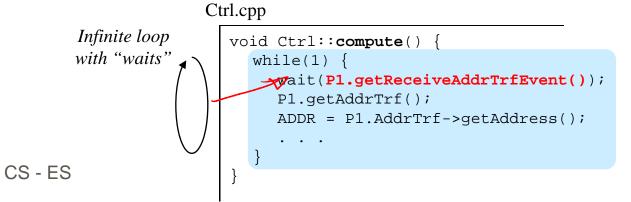

## **SC\_METHOD**

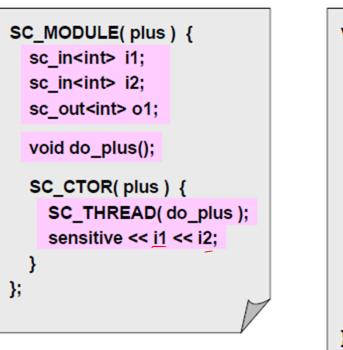

## SC\_THREAD

### **Static Sensitivity**

- Explicit sensitivity list in constructor

- Process declared as SC\_METHOD()

- Connectivity is known only after construction, EventFinder find the relevant event and connect to it

#### **Sensitivity with Clock**

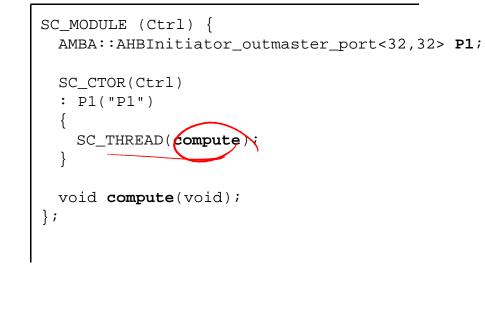

#### Ctrl.h

CS - ES

Dynamic Sensitivity

Process declared as SC\_THREAD()

Use wait() statement in the process

wait( P1.getSendAddrTrfEvent() );

#### **Example: Dynamic Sensitivity**

## Comparison

## **Dynamic Sensitivity**

- wait()

- only for SC\_THREADS and SC\_CTHREADS !!

- wait(e1);

- I waiting for e1 or e2

- wait( e1 | e2 );

- I waiting foe e1 and e2

- wait( e1 & e2);

- // wait 200 ns

- wait( 200, SC\_NS);

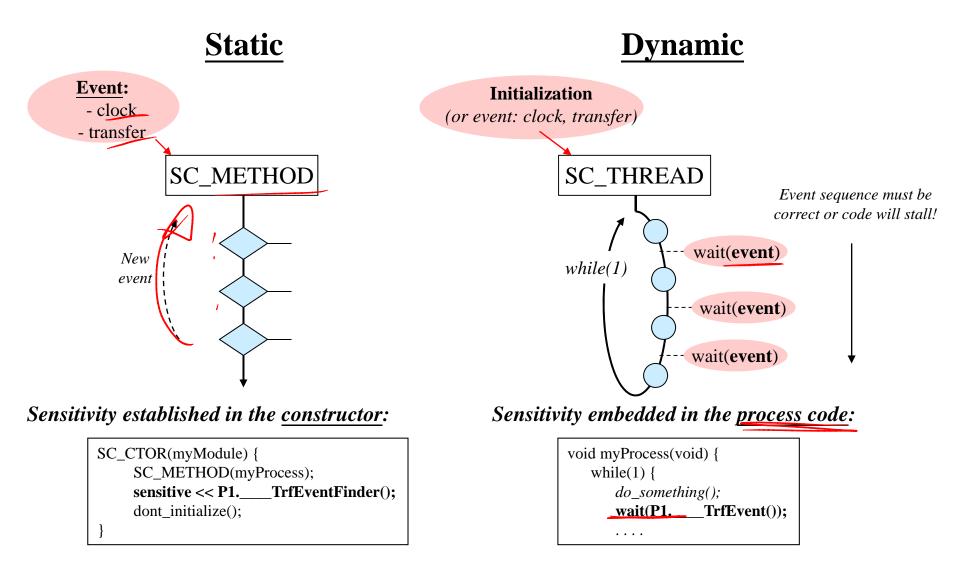

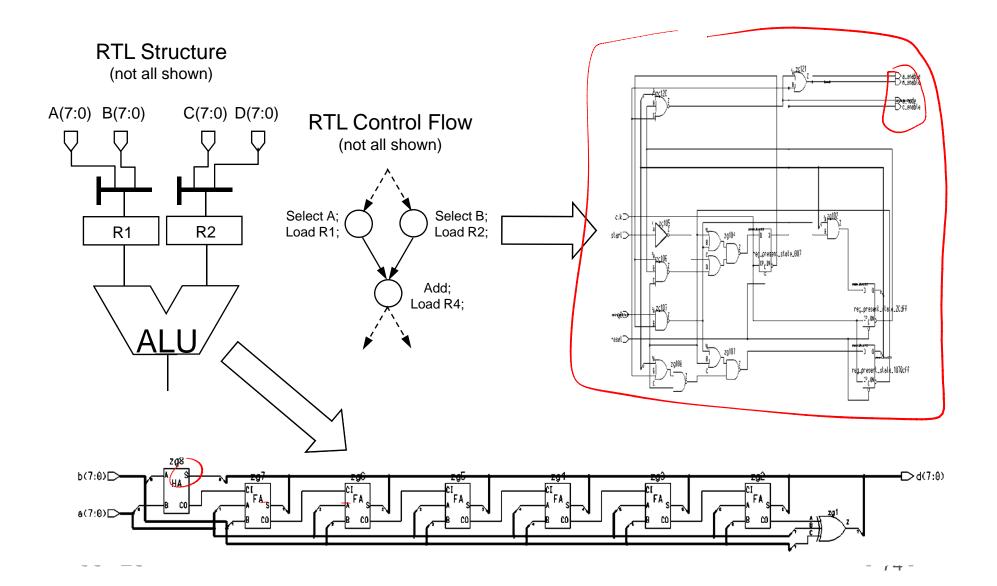

# **Behavioral VS RTL-level Modeling**

- Behavioral-level

- Don't care about states, registers etc.

- Use I/O-cycles

- Think your design as program flow

- RTL-level

- Map different states, registers etc.

- Use clock-cycles

- Think your design as finite- state-machine

# **RTL Level Synthesis**

## **Logic Synthesis**

# **Untimed Functional Modeling**

- Model of computation is KPN

- Communication is handled through limited size FIFO-channels with blocking read() and write() operations

- Algorithmic delays are represented by initial values stored in FIFOs

- Use modules that contain SC\_THREAD processes

- No time will be present, everything advances in delta cycles

- Synchronization is implicit

- Write access block until space is available

- Read access block until data is available

- Caution

- Provide initial values of FIFOs prior simulation

- Make sure that data is produced before it is consumed

# **Timed functional models**

- Notion of time is needed when functional models are used on lower level of abstraction

- Processing delays are done with wait(sc\_time)

- Timed and untimed models can peacefully coexist and interact

- It is even possible to mix FIFO-and signal-based communication

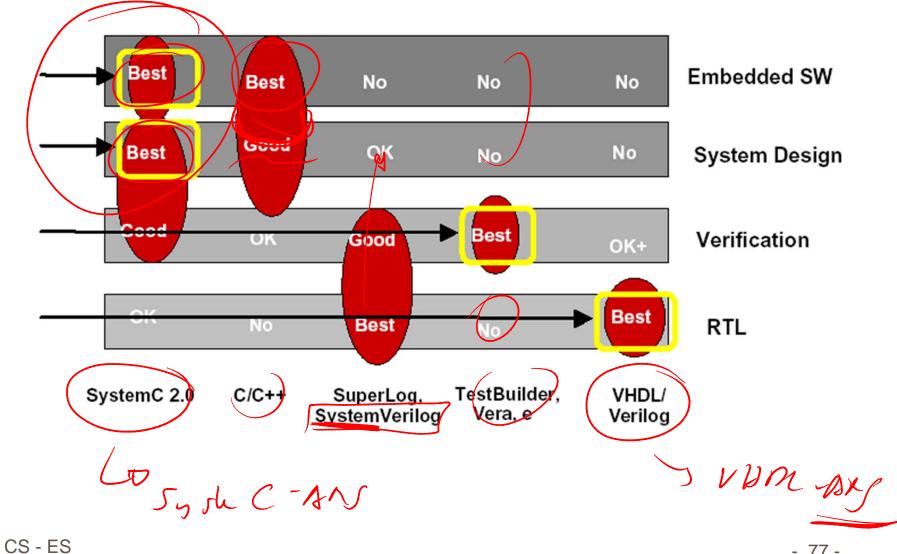

### Hardware description languages

- 77 -

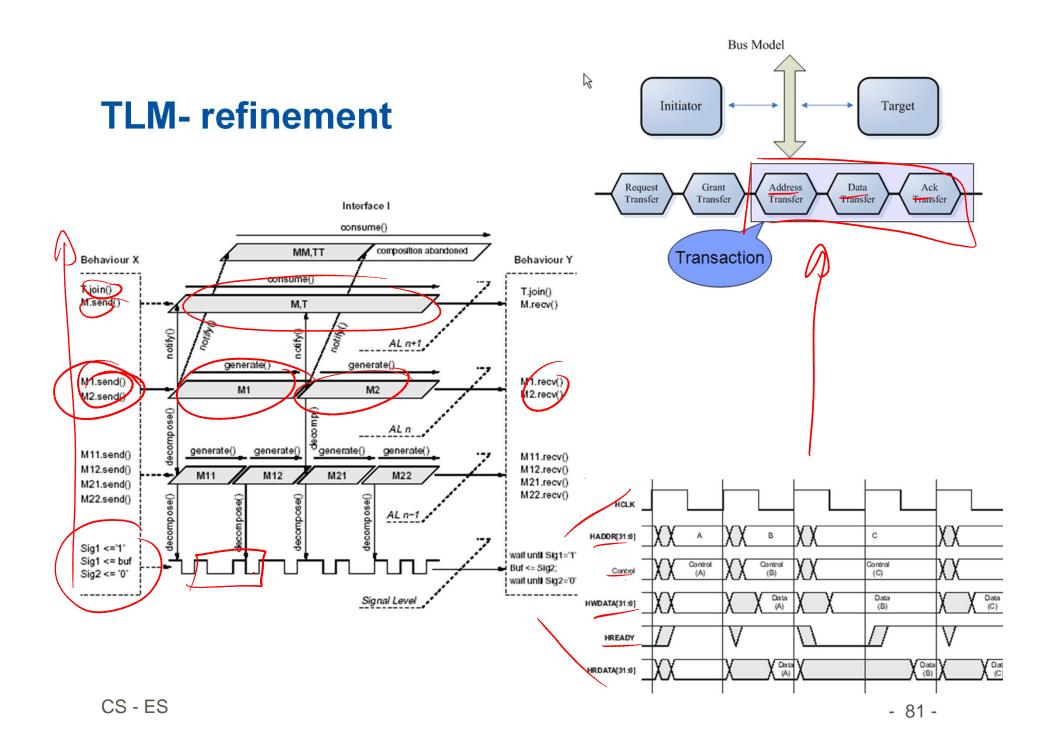

# **SystemC – Transaction level modeling**

# Concept of TLM

- Event-driven simulation style

- That's the name "Transaction"

- Simulation triggered by data communication

- Bus events

- Goal

- High speed simulation

- Simplify modeling

- Early system analysis

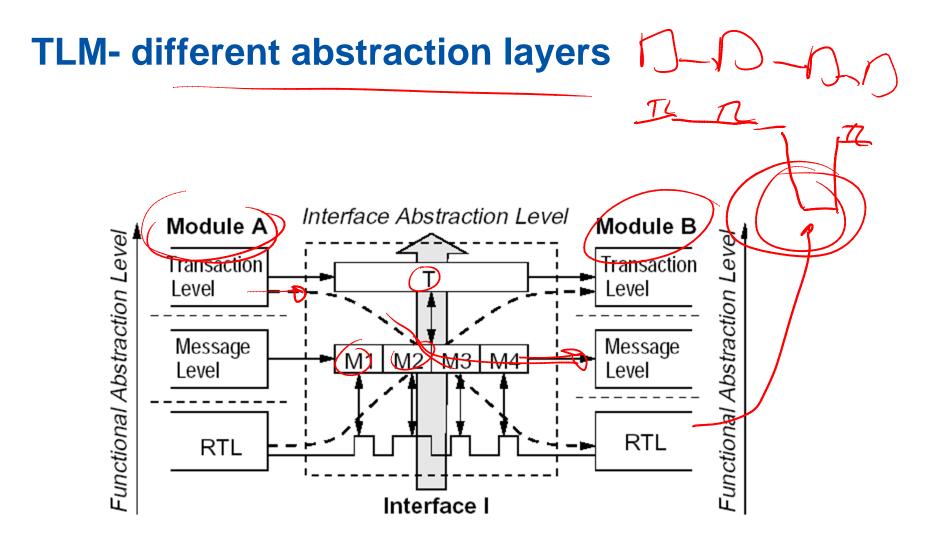

- In a transaction-level model (TLM), the details of communication among computation components are separated from the details of computation components.

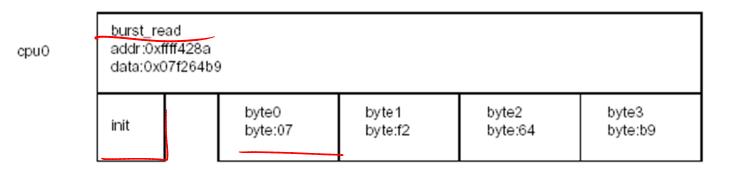

# **Transaction Level Modeling**

- Transaction-level modeling allows faster simulations than pin-based interfaces

- e.g. large burst-mode transfer may take many actual clock cycles, here we can use burst\_read and burst\_write methods

- Use transaction-level modeling when it is beneficial

- functional modeling (untimed and timed)

- platform modeling

- test benches

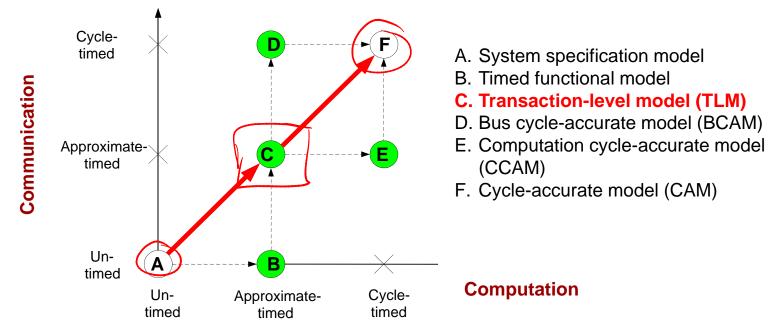

# **Abstraction Levels**

- Abstraction based on level of detail & granularity

- Computation and communication

- System design flow

- Path from model A to model F

#### • Design methodology and modeling flow

• Set of models and transformations between models

# Referenzen

- SystemC Quickreference

- http://comelec.enst.fr/hdl/sc\_docs/systemc\_quickreference.pdf

- ASIC World SystemC Tutorial:

- <u>http://www.asic-world.com/systemc/tutorial.html</u>

- Codebeispiele

- SystemC Einführung

- SystemC Introduction, W.Yang, Dynalith Systems, 2006

- SystemC, TLM (Transaktionsebene) Tutorials, SystemC Verifcation Library

- <u>http://www.doulos.com/knowhow/systemc/</u>

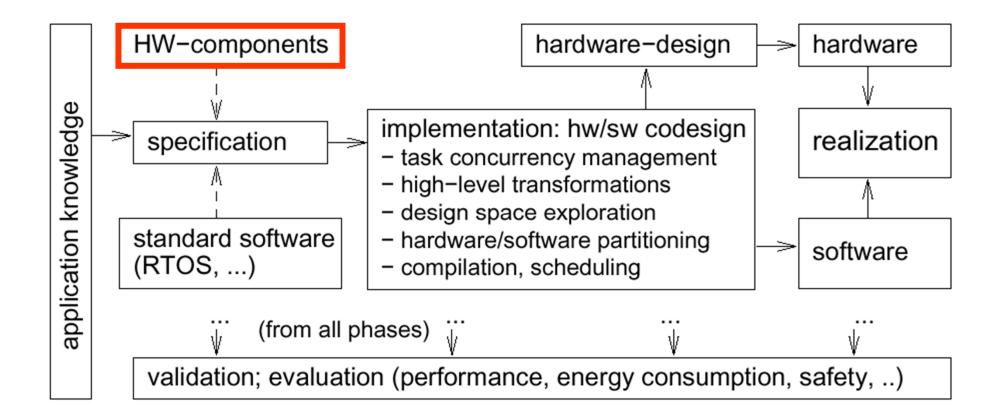

## **Overview of embedded systems design**