#### Midterm exam Thursday May 31, 16:00-18:00

- **Groups 1 12**: HS 002

- All other groups: Günter Hotz lecture hall

- The exam will be open book. That is, you are allowed to use printouts of the lecture slides, books, and any handwritten notes during the exam.

- No discussion slots next week

- Last two problem sets will be discussed in Tutorial on Wednesday

BF - ES - 2 -

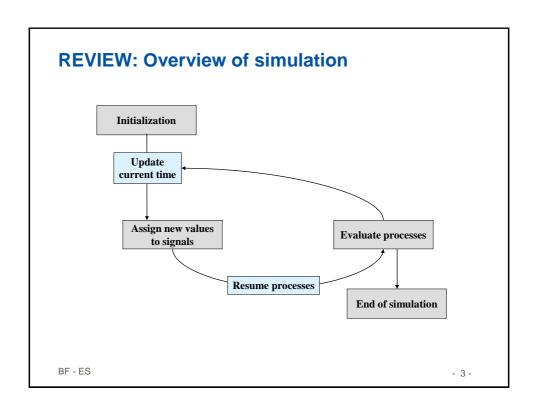

# **REVIEW: Transaction list and process activation list**

- Transaction list

- For signal assignments

- Entries of form (s, v, t) meaning "signal s is set to value v at time t"

- Example: (clock, '1', 10 ns)

- Process activation list

- For reactivating processes

- Entries of form (p<sub>j</sub>, t) meaning "process p<sub>i</sub> resumes at time t".

BF - ES - 4 -

#### **REVIEW: Initialization**

- At the beginning of initialization, the current time,  $t_{curr}$ is assumed to be 0 ns.

- An initial value is assigned to each signal.

- Taken from declaration, if specified there, e.g.,

- signal s : std\_ulogic := `0`;

- Otherwise: First value in enumeration for enumeration based data types, e.g.

- signal s : std\_ulogic type std\_ulogic, is ('U', `X', `0', `1', `Z', `W', `L', `H', `-'); initial value is `U'

- This value is assumed to have been the value of the signal for an infinite length of time prior to the start of the simulation.

- Initialization phase executes each process exactly once (until it suspends).

- During execution of processes: Signal assignments are collected in transaction list (**not** executed immediately!) – more details later.

- If process stops at "wait for"-statement, then update process activation list more details later.

- After initialization the time of the next simulation cycle (which in this case is the first simulation cycle),  $t_{next}$  is calculated:

- Time  $t_{\text{next}}$  of the next simulation cycle = earliest of 1. time high (end of simulation time).

- Earliest time in transaction list (if not empty)

Earliest time in process activation list (if not empty).

BF - ES

- 5 -

#### **REVIEW: Signal assignment phase –** first part of step

- Each simulation cycle starts with setting the current time to the next time at which changes must be considered:

- $t_{curr} = t_{next}$

- This time t<sub>next</sub> was either computed during the initialization or during the last execution of the simulation cycle. Simulation terminates when the current time would exceed its maximum, time'high.

- For all (s, v,  $t_{curr}$ ) in transaction list:

- Remove (s, v, t<sub>curr</sub>) from transaction list.

- s is set to v.

- For all processes p<sub>i</sub> which wait on signal s:

- Insert (p<sub>i</sub>, t<sub>curr</sub>) in process activation list.

- Similarly, if condition of "wait until"-expression changes value.

BF - FS - 6 -

### REVIEW: Process execution phase – second part of step (1)

- Resume all processes p<sub>i</sub> with entries (p<sub>i</sub>, t<sub>curr</sub>) in process activation list.

- Execute all activated processes "in parallel" (in fact: in arbitrary order).

- Signal assignments

- are collected in transaction list (**not** executed immediately!).

- Examples:

- s <= a and b;

- Let v be the conjunction of current value of a and current value of b.

- Insert (s, v,  $t_{curr}$ ) in transaction list.

- s <= '1' **after** 10 ns;

- Insert (s, '1',  $t_{curr}$  + 10 ns) into transaction list.

- Processes are executed until wait statement is encountered.

- If process p<sub>i</sub> stops at "wait for"-statement, then update process activation list:

- Example:

- p<sub>i</sub> stops at "wait for 20 ns;"

- Insert (p<sub>i</sub>, t<sub>curr</sub> + 20 ns) into process activation list

BF - ES - 7 -

## REVIEW: Process execution phase – second part of step (2)

If some process reaches last statement and

- does not have a sensitivity list and

- last statement is not a wait statement,

then it continues with first statement and runs until wait statement is reached.

- When all processes have stopped, the time of the next simulation cycle  $t_{next}$  is calculated:

- Time  $t_{next}$  of the next simulation cycle = earliest of

- 1.time high (end of simulation time).

- 2. Earliest time in transaction list (if not empty)

- 3. Earliest time in process activation list (if not empty).

- Stop if  $t_{next}$  = time'high and transaction list and process activation list are empty.

BF - ES - 8 -

4

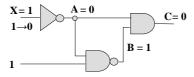

#### **REVIEW: Delta delay**

Simulation time does not proceed due to delta delays!

| Current time | Delta delay | Event                      |

|--------------|-------------|----------------------------|

| 0 ns         | 1           | evaluation of inverter     |

|              |             | (A, 1, 0 ns)               |

|              | 2           | evaluation of AND and NAND |

|              |             | (B, 0, 0ns), (C, 1, 0ns)   |

|              | 3           | evaluation of AND          |

|              |             | (C, 0, 0ns)                |

BF-ES - 9-

#### "Write-write-conflicts"

# signal s : bit; ... p : process begin ... s <= `0`; ... s <= `1`; wait for 5 ns; end process p;

#### Case 1:

Write-write-conflicts are restricted to the same process (i.e. they occur inside the same process)

- Then the second signal assignment overwrites the first one.

- This is the only case of "non-concurrency" of signal assignments

- Note that writing to different signals occurs concurrently, however!

BF - ES - 10 -

#### "Write-write-conflicts"

```

signal s : dt,

...

S<= V<sub>1</sub>;

...

p : process

begin

...

s <= V<sub>2</sub>;

...

end process p;

q : process

begin

...

s <= V<sub>3</sub>;

...

end process q;

```

- Case 2: Write-write-conflicts between different processes

- If there is no "resolution function" for the data type dt, then writing the same signal by different processes in the same step is forbidden.

- If there is a resolution function, then the resolution function computes the value of s at time t<sub>curr</sub>:

- Value for s in the current step is computed for each process separately,

- resolution function is used to compute final result.

BF - ES - 11 -

#### Abstraction of electrical signals

- Complete analog simulation at the circuit level would be time-consuming

- The We try to use digital values and DE simulation as long as possible

- Flowever, using just 2 digital values would be too restrictive

- We introduce the distinction between:

- the logic level (as an abstraction of the voltage) and

- the strength (as an abstraction of the current drive capability) of a signal.

- The two are encoded in logic values.

BF - ES - 12 -

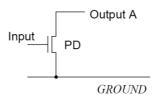

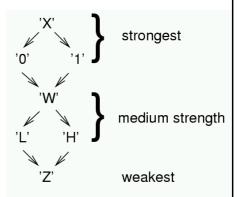

#### 1 signal strength

- Logic values '0' and '1'.

- Both of the same strength.

- Encoding false and true, respectively.

BF - ES - 13 -

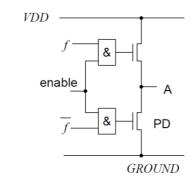

#### 2 signal strengths

- Many subcircuits can effectively disconnect themselves from the rest of the circuit (they provide "high impedance" values to the rest of the circuit).

- Example: subcircuits with open collector

VDD —

Input = '0' -> A disconnected

BF - ES - 14 -

#### **TriState circuits**

enable = '0' -> A disconnected

Two we introduce signal value 'Z', meaning "high impedance"

BF - ES - 15

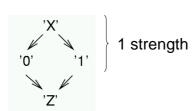

#### 2 signal strengths (cont'ed)

- We introduce an operation #, which generates the effective signal value whenever two signals are connected by a wire.

- #('0','Z')='0'; #('1','Z')='1'; '0' and '1' are "stronger" than 'Z'

Hasse diagram

BF - ES

According to the partial order in the diagram, # returns the smallest element at least as large as the *two arguments* ("Sup").

In order to define #('0','1'), we introduce 'X', denoting an undefined signal level.

'X' has the same strength as '0' and '1'.

- 16 -

8

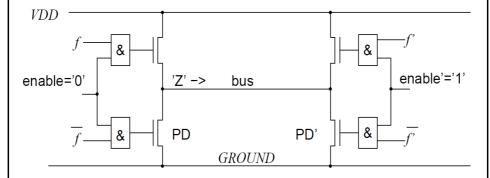

#### **Application example**

signal value on bus = #(value from left subcircuit, value from right subcircuit)

#('Z', value from right subcircuit) = value from right subcircuit "as if left circuit were not there".

BF - ES - 17 -

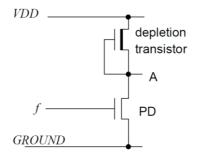

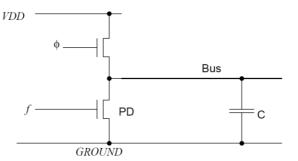

#### 3 signal strengths

Depletion transistor contributes a weak value to be considered in the #-operation for signal A

Introduction of 'H',

denoting a weak signal of the same level as '1'.

$\#('H', '0')='0'; \ \#('H', 'Z')='H'$

BF - ES - 18 -

#### 3 signal strengths

- There may also be weak signals of the same level as '0'

- Introduction of 'L', denoting a weak signal of the same level as '0': #('L', '1')='1'; #('L', 'Z') = 'L';

- Introduction of 'W', denoting a weak signal of undefined level 'X': #('L', 'H')='W'; #('L','W') = 'W';

- # reflected by the partial order shown.

BF - ES

- 19 -

#### 4 signal strengths (1)

pre-charging:

Pre-charged '1'-levels weaker than any of the values considered so far, except 'Z'.

Introduction of 'h', denoting a very weak signal of the same level as '1'.

BF - ES

- 20 -

#### 4 signal strengths (2)

- There may also be weak signals of the same level as '0'

- Introduction of 'I', denoting a very weak signal of the same level as '0': #('I', '0')='0'; #('I,'Z') = 'I';

- Introduction of 'w', denoting a very weak signal of the same level as 'W': #('I', 'h')='w'; #('h', 'w') ='w'; ...

- # reflected by the partial order shown.

BF - ES - 21 -

#### **IEEE 1164**

- VHDL allows user-defined value sets.

- → Each model could use different value sets (unpractical)

- → Definition of standard value set according to standard IEEE 1164:

- First seven values as discussed previously.

- 'U': un-initialized signal; used by simulator to initialize all not explicitly initialized signals: **type** std\_ulogic **is** (`U`, `X`, `0`, `1`, `Z`, `W`, `L`, `H`, `-`);

- '-': is used to specify don't cares:

- Example: if a /= '1' or b/='1' then f <= a exor b; else f <= '-';</p>

- '-' may be replaced by arbitrary value by synthesis tools.

BF - FS - 22 -

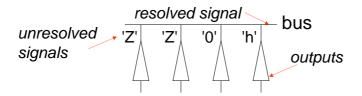

#### **Outputs tied together**

In hardware, connected outputs can be used:

```

Modeling in VHDL: resolution functions

type std_ulogic is ('U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-');

subtype std_logic is resolved std_ulogic;

```

BF - ES - 23 -

#### **Resolution function for IEEE 1164**

BF - ES

```

type std_ulogic_vector is array(natural range<>)of std_ulogic;

function resolved (s:std_ulogic_vector) return std_logic is

variable result: std_ulogic:='Z'; --weakest value is default

begin

if (s'length=1) then return s(s'low) --no resolution

else for i in s'range loop

result:=resolution_table(result,s(i))

end loop

end if;

return result;

end resolved;

```

12

- 24 -

#### **Resolution function for IEEE 1164**

```

constant resolution_table : stdlogic_table := (

Z W

Χ

0

1

H -

('U', 'U', 'U', 'U', 'U', 'U',

'U', 'U', 'U'),

--| U |

'X', 'X', 'X'),

('U', 'X', 'X', 'X', 'X', 'X',

--| X |

('U', 'X',

'0', 'X', '0', '0',

'0', '0', 'X'),

--| 0 |

'X', '1', '1', '1',

('U', 'X',

'1', '1', 'X'),

--| 1 |

'1', 'Z', 'W',

('U', 'X',

'0',

'L', 'H', 'X'),

--| Z |

'0',

'1', 'W', 'W',

'W', 'H', 'X'),

('U', 'X',

--| W |

('U', 'X',

'0', '1', 'L', 'W',

'L', 'W', 'X'),

--| L |

('U', 'X', '0', '1', 'H', 'W',

'W', 'H', 'X'),

--| H |

('U', 'X', 'X', 'X', 'X', 'X',

'X', 'X', 'X')

--| - |

);

BF - ES

- 25 -

```

#### Inertial and transport delay model

- Signal assignment:

- signal\_assignment ::=

target <= [ delay\_mechanism ] waveform\_element

{ , waveform\_element }</pre>

- waveform\_element ::= value\_expression [ after time\_expression ]

- delay\_mechanism ::= transport | [ reject time\_expression ] inertial

- Example:

- Inpsig <= '0', '1'after 5 ns, '0' after 10 ns, '1' after 20 ns;</li>

BF - ES - 26 -

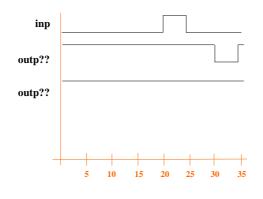

#### Inertial and transport delay model

Example for signal assignment: outp <= not inp after 10 ns;</p>

BF - ES

- 27 -

#### Inertial and transport delay model

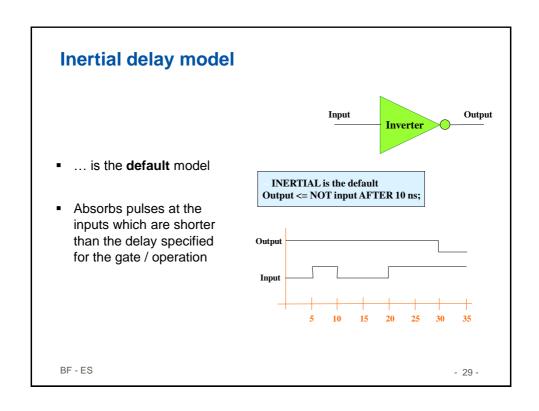

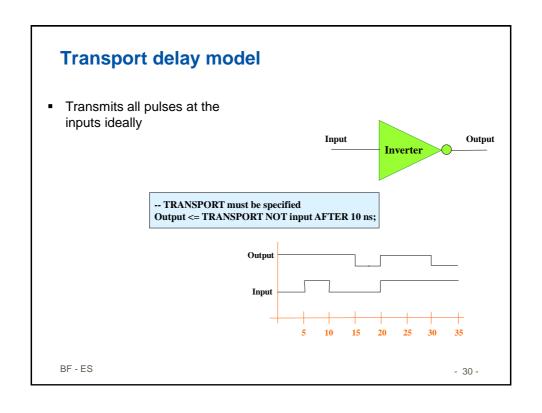

Two delay models in VHDL:

- Inertial delay ("träge Verzögerung")

- Transport delay ("nichtträge Verzögerung")

Inertial delay model is motivated by the fact that physical gates absorb short pulses (spikes) at their inputs (due to internal capacities)

BF - ES

- 28 -

#### Inertial and transport delay model entity DELAY is end DELAY; p1: process architecture RTL of DELAY is begin signal A, B, X, Y: bit; A <= '0', '1' after 20 ns, '0' after 40 ns, '1' after 60 ns; begin B <= '0', '1' after 30 ns, '0' p0: process (A, B) begin after 35 ns, '1' after 50 ns; Y <= A nand B after 10 ns; wait for 80 ns; X <= transport A nand B after 10 ns; end process end process; end RTL; A В X BF - ES - 31 -

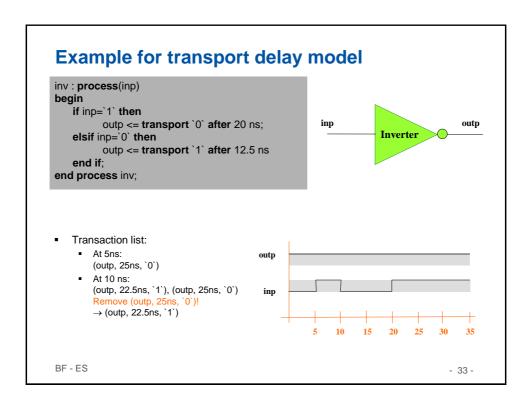

#### Semantics of transport delay model

Signal assignments change transaction list.

Before transaction (s, t₁, v₁) is inserted into transaction list, all transactions in the transaction list (s, t₂, v₂) with t₂ ≥ t₁ are removed from transaction list.

BF - ES - 32 -

#### Semantics of inertial delay model

- Semantics for more general version of inertial delay statement:

- Inertial delay absorbs pulses at the inputs which are shorter than the delay specified for the gate / operation.

- Key word reject permits absorbing only pulses which are shorter than specified delay:

- · Example:

- outp <= reject 3 ns inertial not inp after 10 ns;</p>

- Only pulses smaller than 3 ns are absorbed.

- outp <= reject 10 ns inertial not inp after 10 ns;</li>

and

outp <= not inp after 10 ns;</li>

are equivalent.

BF - ES - 34 -

#### Semantics of inertial delay model

- Rule 1 as for transport delay model:

Before transaction (s, t₁, v₁) is inserted into transaction list, all transactions in the transaction list (s, t₂, v₂) with t₂ ≥ t₁ are removed from transaction list.

- Rule 2 removes also some transactions with times < t<sub>1</sub>:

- Suppose the time limit for reject is rt.

- Transactions for signal s with time stamp in the intervall (t<sub>1</sub> rt, t<sub>1</sub>) are removed.

- Exception: If there is in (t<sub>1</sub> – rt, t<sub>1</sub>) a subsequence of transactions for s immediately before (s, t<sub>1</sub>, v<sub>1</sub>) which also assign value v<sub>1</sub> to s, then these transactions are preserved.

BF - ES - 35 -

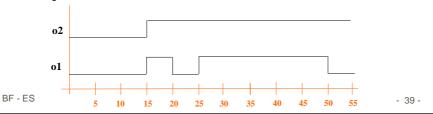

#### **Example**

Transaction list until "wait for 15 ns":

(01, 0ns, '0'), (01, 5ns, '0'), (01, 15ns, '1'), (01, 20ns, '0'), (01, 25ns, '1'), (01, 30ns, '1'), (01, 45ns, '1'), (01, 50ns, '0'), (02, 0ns, '0'), (02, 5ns, '0'), (02, 15ns, '1'), (02, 20ns, '0'), (02, 25ns, '1'), (02, 30ns, '1'), (02, 45ns, '1'), (02, 50ns, '0')

Transaction list when process is reactivated at time 15ns:

(o1, 20ns, `0`), (o1, 25ns, `1`), (o1, 30ns, `1`), (o1, 45ns, `1`), (o1, 50ns, `0`), (o2, 20ns, `0`), (o2, 25ns, `1`), (o2, 30ns, `1`), (o2, 45ns, `1`), (o2, 50ns, `0`)

BF - ES - 36 -

#### **Example**

```

process

begin

o1 <= transport '0', '0' after 5ns, '1' after 15 ns, '0' after 20ns,

`1` after 25 ns, `1` after 30ns, `1` after 45 ns,

`0` after 50 ns;

-- same signal assignment for o2

o2 <= transport '0', '0' after 5ns, '1' after 15 ns, '0' after 20ns,

`1` after 25 ns, `1` after 30ns, `1` after 45 ns,

'0' after 50 ns;

wait for 15 ns;

o2 <= reject 22 ns inertial `1` after 25 ns;

wait.

end process;

At time 15ns:

insert transaction (o2, 40ns, `1`).

```

- Remove transactions with time stamp ≥ 40ns.

- Results in preliminary transaction list: (a1, 20ns, '0'), (a1, 25ns, '1'), (a1, 30ns, '1'), (a1, 45ns, '1'), (a1, 50ns, '0'), (a2, 20ns, '0'), (a2, 25ns, '1'), (a2, 30ns, '1'), (a2, 40ns, '1')

BF - ES

- 37 -

#### **Example**

```

process

begin

o1 <= transport '0', '0' after 5ns, '1' after 15 ns, '0' after 20ns,

`1` after 25 ns, `1` after 30ns, `1` after 45 ns,

'0' after 50 ns:

-- same signal assignment for o2

o2 <= transport `0`, `0` after 5ns, `1` after 15 ns, `0` after 20ns,

`1` after 25 ns, `1` after 30ns, `1` after 45 ns,

`0` after 50 ns;

wait for 15 ns;

o2 <= reject 22 ns inertial `1` after 25 ns;

wait;

end process;

```

- Results in preliminary transaction list: (o1, 20ns, `0'), (o1, 25ns, `1'), (o1, 30ns, `1'), (o1, 45ns, `1'), (o1, 50ns, `0'), (o2, 20ns, `0'), (o2, 25ns, `1'), (o2, 30ns, `1'), (o2, 40ns, `1')

- Rule 2:

- (o2, 25ns, `1`), (o2, 30ns, `1`) are preserved, (o2, 20ns, `0') is removed.

- Resulting transaction list: (o1, 20ns, °0'), (o1, 25ns, °1'), (o1, 30ns, °1'), (o1, 45ns, °1'), (o1, 50ns, °0'), (o2, 25ns, °1'), (o2, 30ns, °1'), (o2, 40ns, °1')

BF - ES

#### Rule 2:

- Transactions for signal o2 with time stamp in the intervall (40ns -22ns, 40ns) = (18ns, 40ns) are removed.

- Exception: If there is in (18ns, 40ns) a subsequence of transactions for o2 immediately before (o2, 40ns, `1`) which also assign value `1` to o2, then these transactions are preserved.

#### **Example**

Resulting wave form:

#### **Functions and procedures**

- Apart from entities / architectures there are also functions and procedures in the usual (software) sense.

- Functions are typically used for providing conversion between data types or for defining operators on userdefined data types.

- Procedures may have parameters of directions in, out and inout.

- in comparable to call by value,

- out for providing results,

- inout comparable to call by reference.

BF - ES - 41 -

# Example architecture RTL of TEST is function BOOL2BIT (BOOL: boolean) return bit is begin if BOOL then return '1'; else return '0'; end if; end BOOL2BIT; procedure EVEN\_PARITY ( signal D: in bit\_vector(7 downto 0); signal PARITY: out bit ) is variable temp: bit; begin .... end; signal DIN: bit\_vector(7 downto 0); signal BOOL1: boolean; signal BIT1, PARITY: bit; begin do\_it: process (BOOL1, DIN) begin BIT1 <= BOOL2BIT(BOOL1); EVEN\_PARITY(DIN, PARITY); end process; .... end; BF-ES

#### **Parameterized hardware**

- Conditional component instantiation with if ... generate construct.

- Iterative component instantiation with for ... generate construct.

- Parameterized design with generic parameters.

BF - ES - 43 -

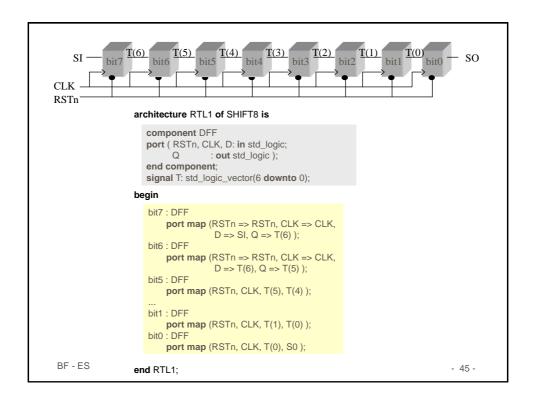

```

Example: 8-bit shift register

SI bit T(6) bit T(5) bit T(4) bit T(2) bit T(1) bit T(0) bit 0 SO

CLK

RSTn

entity SHIFT8 is port (RSTn, CLK, SI: in std_logic; SO: out std_logic); end SHIFT8;

BF-ES

```

#### **Example: 1024-bit shift register** architecture RTL2 of SHIFT1024 is component DFF port ( RSTn, CLK, D: in std\_logic; Q : out std\_logic ); end component; signal T: std\_logic\_vector(1022 downto 0); g0: for i in 1023 downto 0 generate g1: if (i = 1023) generate bit1023: DFF port map (RSTn,CLK,SI,T(1022)); end generate; g2: if (i>0) and (i<1023) generate bitm : DFF port map (RSTn,CLK,T(i),T(i-1)); end generate; g3: if (i=0) generate bit0 : DFF port map (RSTn,CLK,T(0),S0); end generate; end generate; end RTL2; BF - ES - 46 -

```

Example: n-bit shift register

entity SHIFTn is

generic ( n : positive);

architecture RTL3 of SHIFTn is

port ( RSTn, CLK, SI : in std_logic;

SO : out std_logic );

component DFF

port ( RSTn, CLK, D: in std_logic;

end SHIFTn;

: out std_logic );

end component;

signal T: std_logic_vector(n-2 downto 0);

g0: for i in n-1 downto 0 generate

g1: if (i = n-1) generate

bit_high: DFF port map (RSTn,CLK,SI,T(n-2));

end generate;

g2: if (i>0) and (i<n-1) generate

bitm: DFF port map (RSTn,CLK,T(i),T(i-1));

end generate;

g3: if (i=0) generate

bit0 : DFF port map (RSTn,CLK,T(0),S0);

end generate;

end generate;

end RTL3;

BF - ES

- 47 -

```

#### **Example: n-bit shift register**

Component instantiation

BF - ES

- 48 -

- 49 -

#### **VHDL: Evaluation**

- Hierarchical specification by entities / architectures / components, (procedures and functions)

- no nested processes

- Static number of processes

- Complicated simulation semantics

- May be too low level for initial, abstract specification of very large systems

- Mainly used for hardware simulation+synthesis

BF - ES

#### **REVIEW: computational models**

| Communication/<br>local computations | Shared memory                                                  | Asynchronous message passing                 |

|--------------------------------------|----------------------------------------------------------------|----------------------------------------------|

| Communicating finite state machines  | Statecharts,<br>hybrid automata,<br>synchronous<br>composition |                                              |

| Data flow                            |                                                                | Petri nets,<br>Kahn process networks,<br>SDF |

| Discrete event (DE) model            | Simulink, VHDL                                                 | Distributed DE                               |

BF - ES - 50 -

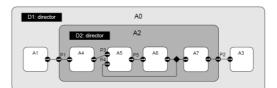

#### **Combinations of computational models**

BF - ES - 51 -

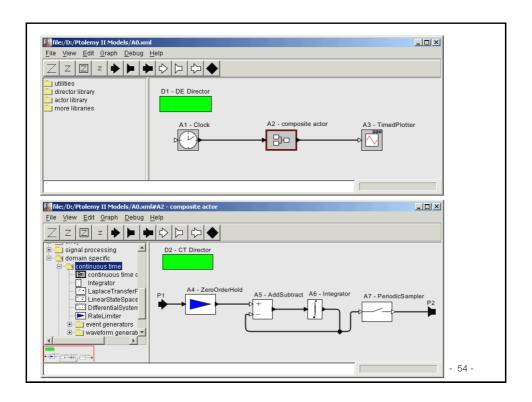

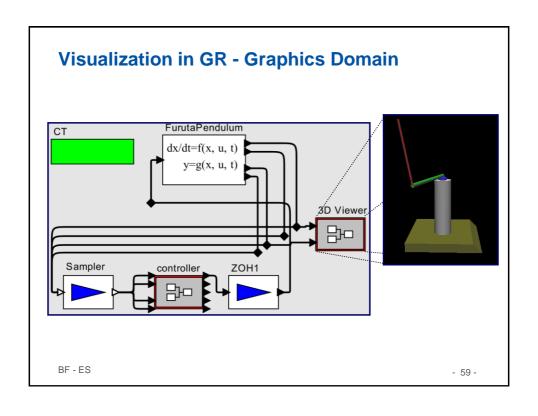

#### **Ptolemy**

Ptolemy (UC Berkeley) is an environment for simulating multiple models of computation.

http://ptolemy.berkeley.edu/

- discrete-event systems

- SDF

- process networks

- Petri nets

- priority-based schedules

- synchronous/reactive

- Finite-state machines

- continuous-time

- modal systems

- Graphics, 3D animations

BF - ES

- 52 -

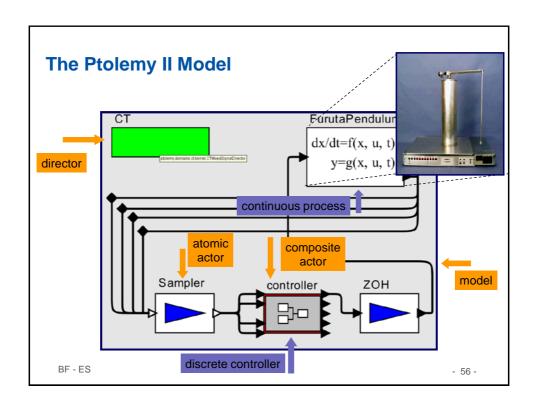

#### **Ptolemy**

- A model is a set of interconnected actors and one director

- Actor

- Input & output ports, states, & parameters

- Models of computation

- Define the interaction semantics

- Implemented in Ptolemy II by a domain

- Director + Receiver

- Director

- Manages the data flow and the scheduling of the actors

- The director fires the actors

- Receiver

- Defines the semantics of the port buffers

BF - ES

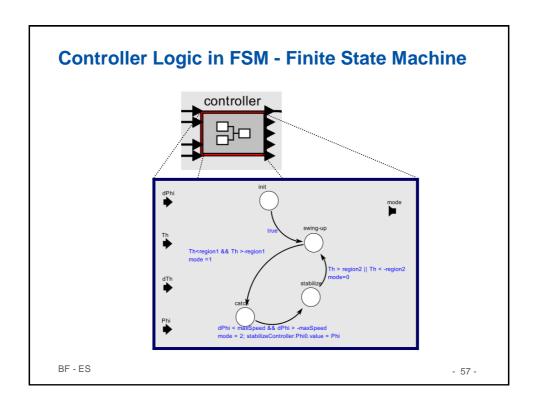

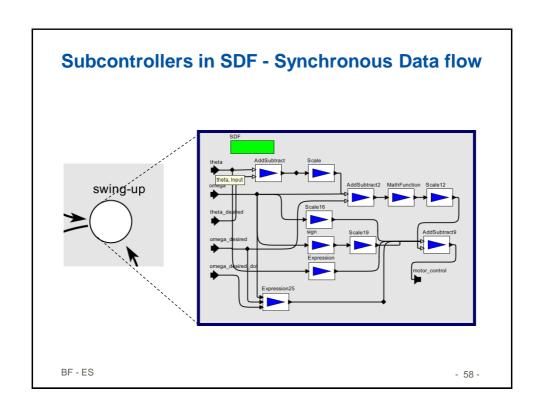

#### **Example: Inverted Pendulum**

- Classic control problem

- Swing up the pendulum and then keep it in the upright position

Heterogeneous Modeling and Design of Control Systems, Liu/Liu/Eker/Lee, 2003

BF - ES

# UML (Focus on support of early design phases)

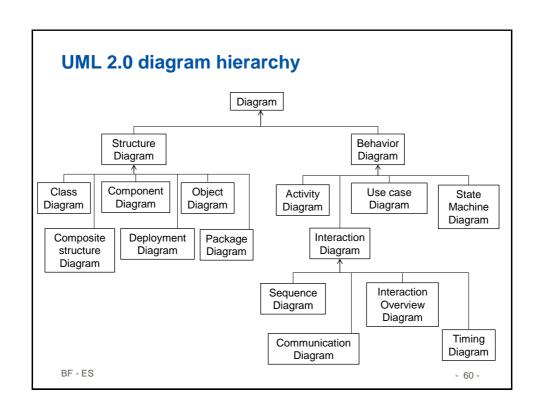

| Communication/<br>local computations | Shared memory  | Asynchronous message passing                          |

|--------------------------------------|----------------|-------------------------------------------------------|

| Communicating finite state machines  | State diagrams |                                                       |

| Data flow                            |                | Activity diagrams, sequence diagrams, timing diagrams |

BF - ES - 61 -

#### **UML** for embedded systems

- Initially not designed for real-time.

- Initially lacking features:

- Partitioning of software into tasks and processes

- specifying timing

- specification of hardware components

- Projects on defining profiles for embedded/real-time systems

- Schedulability, Performance and Timing Analysis

- SysML (System Modeling Language)

- UML Profile for SoC

- Modeling and Analysis of Real-Time Embedded Systems

- UML/SystemC, ...

- Profiles may be incompatible

BF - ES - 62 -