| Communication/<br>local computations      | Shared memory                                                  | Asynchronous message passing                 |

|-------------------------------------------|----------------------------------------------------------------|----------------------------------------------|

| Communicating<br>finite state<br>machines | Statecharts,<br>hybrid automata,<br>synchronous<br>composition |                                              |

| Data flow                                 |                                                                | Petri nets,<br>Kahn process networks,<br>SDF |

| Discrete event (DE)<br>model              | Simulink, VHDL                                                 | Distributed DE                               |

| Scheduling strategy                   | Code  | Data |

|---------------------------------------|-------|------|

| Minimum buffer schedule, no looping   | 13735 | 32   |

| Minimum buffer schedule, with looping | 9400  | 32   |

| Worst minimum code size schedule      | 170   | 1021 |

| Best minimum code size schedule       | 170   | 264  |

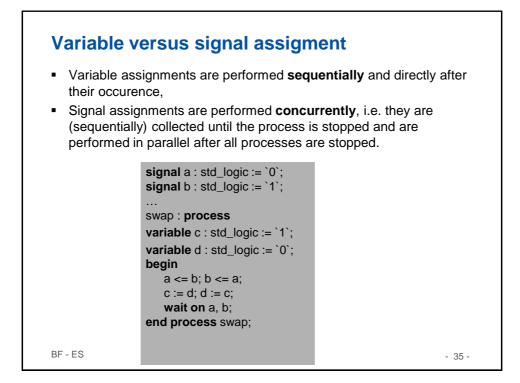

| Example                                                                                                                                                                                                                                  |        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| <pre>architecture behaviour of example is     signal a : std_logic := `0`;     signal b : std_logic := `1`;     signal c : std_logic := `1`;     signal d : std_logic := `0`;     begin         swap1: process(a, b)         begin</pre> |        |

| swap2: process<br>begin<br>c <= d;<br>d <= c;<br>wait for 15 ns;<br>end process;<br>end architecture;                                                                                                                                    |        |

| BF - ES                                                                                                                                                                                                                                  | - 40 - |

| Example                                                                                                                                                                                                                                                                      |        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| architecture behaviour of example is<br>signal a : std_logic := `0`;<br>signal b : std_logic := `1`;<br>signal c : std_logic := `1`;<br>signal d : std_logic := `0`;<br>begin<br>swap1: process(a, b)<br>begin<br>a <= b after 10 ns;<br>b <= a after 10 ns;<br>end process; |        |

| swap2: process<br>begin<br>c <= d;<br>d <= c;<br>wait for 15 ns;<br>end process;<br>end architecture;                                                                                                                                                                        |        |

| BF - ES                                                                                                                                                                                                                                                                      | - 42 - |

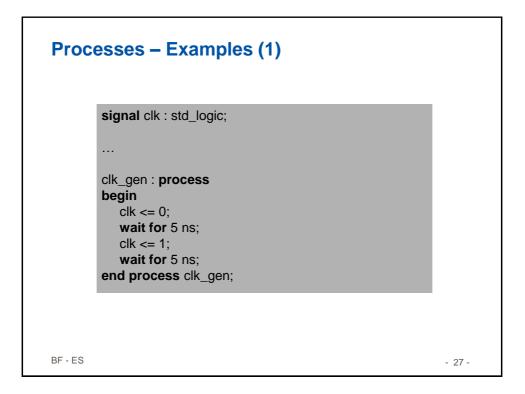

## **Example**

```

architecture behaviour of example is

signal a : std_logic := `0`;

signal b : std_logic := `1`;

signal c : std_logic := `1`;

signal d : std_logic := `0`;

begin

swap1: process(a, b)

begin

a <= b after 10 ns;

b <= a after 10 ns;

end process;

swap2: process

begin

c <= d;

d <= c;

wait for 15 ns;

end process;

end architecture;

BF - ES

```

- 45 -